A fan-out package and manufacturing method thereof

A manufacturing method and packaging technology, applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., can solve problems such as high parasitic capacitance and inductance, deformation and fracture of passivation layer, signal short circuit, etc., to improve quality and protection ability The effect of improving and increasing firmness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

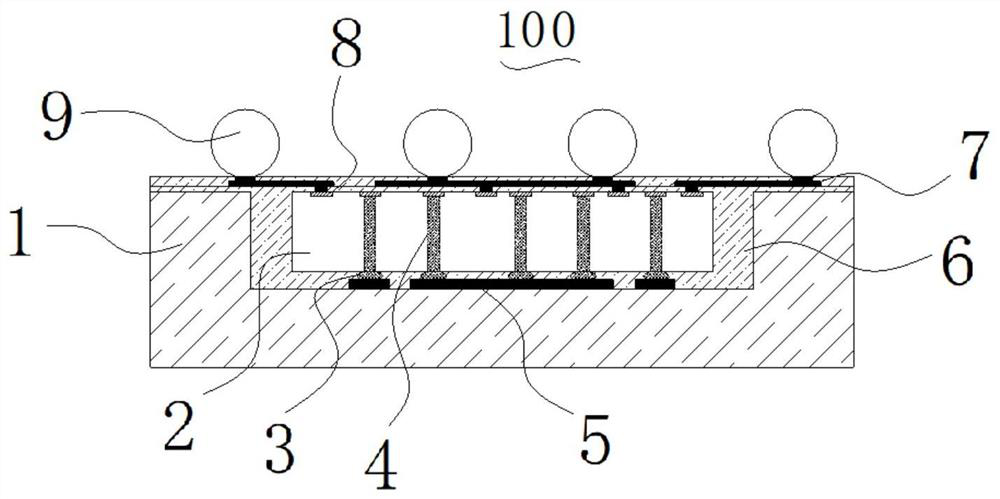

[0045] See figure 2 , figure 2 It is a schematic diagram of the fan-out package structure in a first embodiment of the present invention. As shown, the fan-out package 100 comprising a substrate 1, chip 2, plastic material 6, a first redistribution layer 7, a second redistribution layer 5, and a plurality of solder balls 9. The substrate 1 is typically a semiconductor material, such as silicon, germanium, selenium, or compound semiconductors, organic semiconductors, with a receiving slot on the substrate, and acting as a support is placed the chip, and to assume a portion of the electrical properties.

[0046] Chip 2 is placed on the receiving groove substrate 1, the chip 2 includes a first surface and a second surface opposite the first surface, the first surface 8 is provided with a plurality of input and output ports, the second surface is provided with a plurality of bumps 3, the bumps 3 of the plurality of positions corresponding to a plurality of input and output ports of at...

no. 2 approach

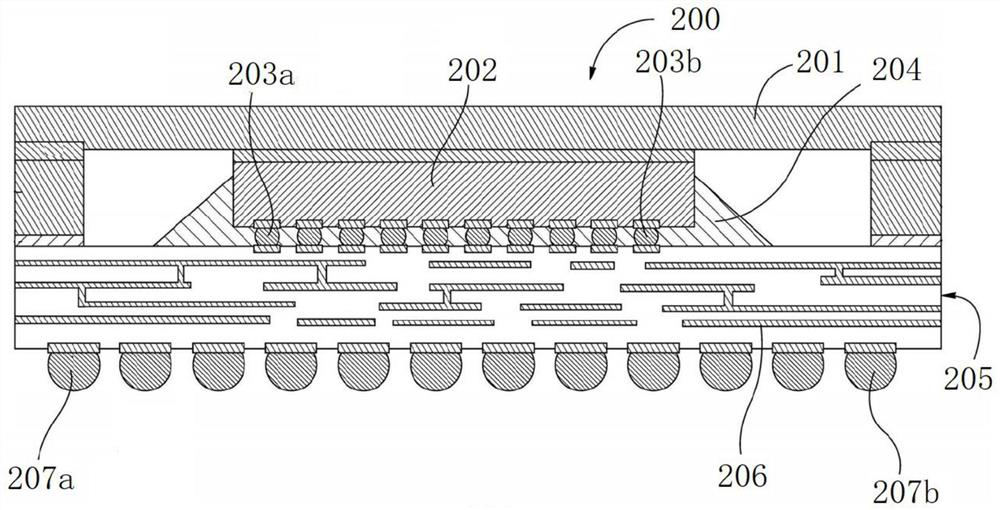

[0064] See Figure 4 , Figure 4 It is a schematic structural diagram of a fan-out package in a second embodiment of the present invention. As shown, in this embodiment, the fan-out package 110 introduces two chips 2a and 2b, each having at least one TSV4 '. The two chips can be a chip of different functions, or the same functional chip, and there is a signal transmission between each other, that is, at least one input / output port of the chip 2a needs to be connected to at least one input and output port of the chip 2b. According to the spirit of the invention, these input and output ports that require interconnect or derive will guide the second surface corresponding to the second surface by TSV4 '.

[0065] In this embodiment, the graphic of the first redistribution layer 7 'and the second redistribution layer 5' needs to guide the first surface to the input and output port 8 'of electrical interconnection or electrical extraction in accordance with the specific circuitry. Exter...

Embodiment approach 2

[0066] The second embodiment gives the package structure of two chips, which should be noted that for two or more multi-chip packages, the invention can also be designed according to the invention of the invention, without the need for creative labor. For the production method of the second embodiment, as the embodiment is substantially the same, only the graphic of the first redistribution layer and the second redistribution layer is designed, the design is required to be designed according to the specific circuitry. The same is the same as the implementation, and will not be described again.

[0067] In summary, the present invention proposes a new fan-out package and a method of fabricating the same, which leads some input and output port ports to the back side by introducing TSV structures in the chip, and then in front of both sides The rearrangement layer structure is designed to reduce the number of redistributed layer metal layers on a single side, thereby reducing the occ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com