Method and system for establishing standard cell library, and chip design method and system

A standard cell library, chip design technology, applied in the direction of CAD circuit design, configuration CAD, etc., can solve problems such as inability to meet various application requirements, waste of resources, and no consideration of products

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0066] In order to make the purpose and features of the present invention more obvious and understandable, the technical solutions of the present invention will be described in detail below in conjunction with the accompanying drawings. However, the present invention can be implemented in different forms and should not be limited to the described embodiments. In addition, it should be noted that the technology of the present disclosure may be implemented in the form of hardware and / or software (including firmware, microcode, etc.).

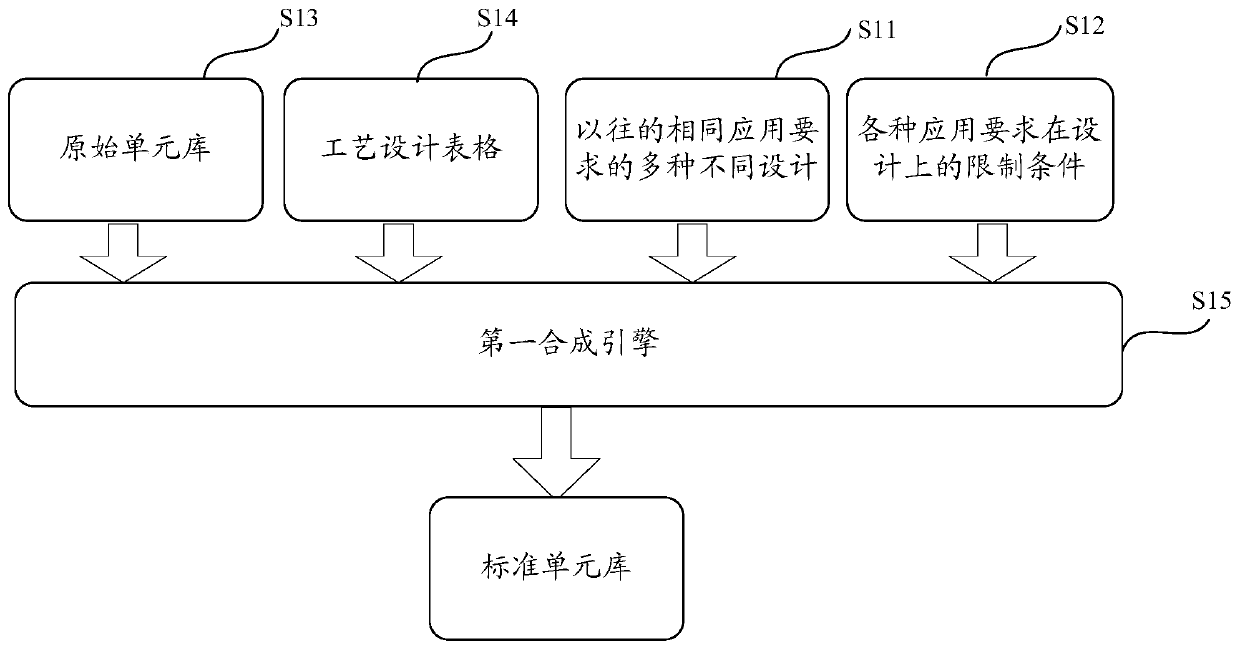

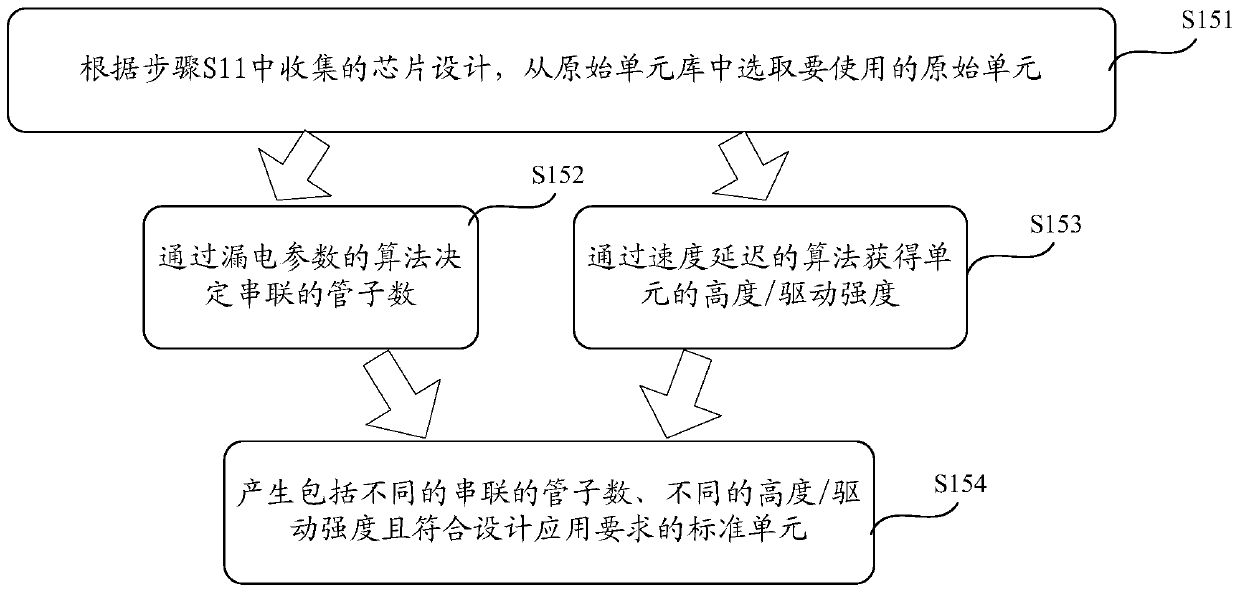

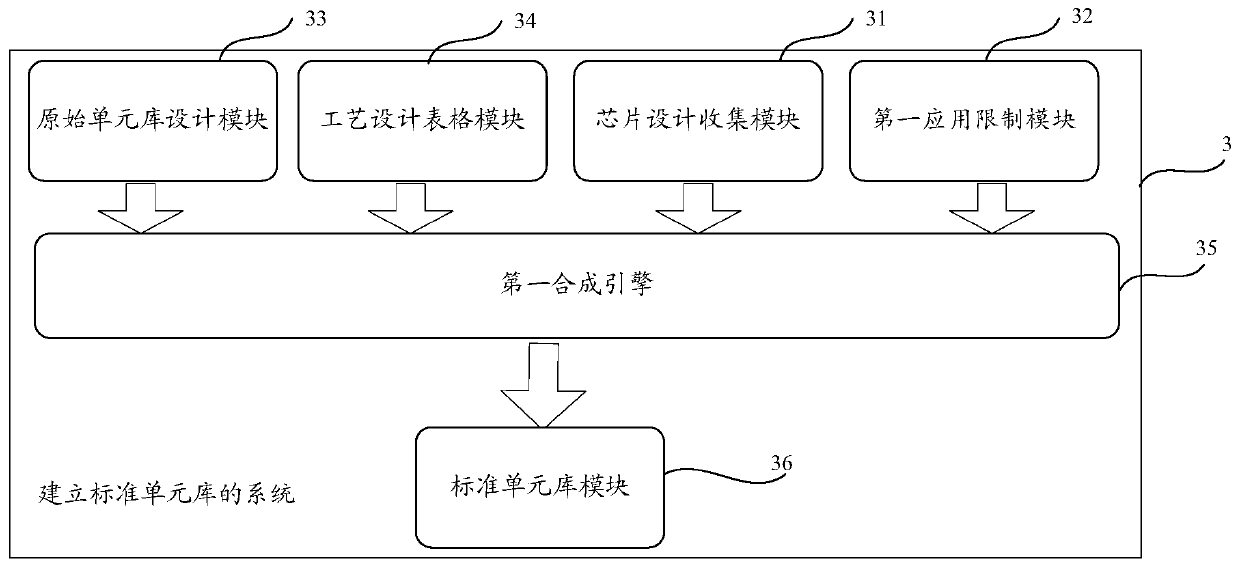

[0067] Please refer to figure 2 , an embodiment of the present invention provides a method for establishing a standard cell library, comprising the following steps:

[0068] S11, obtaining multiple different chip designs for the same application requirements in the past;

[0069] S12. Obtain the design constraints of each of the application requirements;

[0070] S13, designing an original cell library with a fixed layout;

[0071] S14, making...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com