Method and system for establishing standard cell library, and chip design method and system

A standard cell library, standard cell technology, applied in computer-aided design, calculation, special data processing applications, etc., can solve problems such as time-consuming and laborious, different standard cell design rules, standard cell rework, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

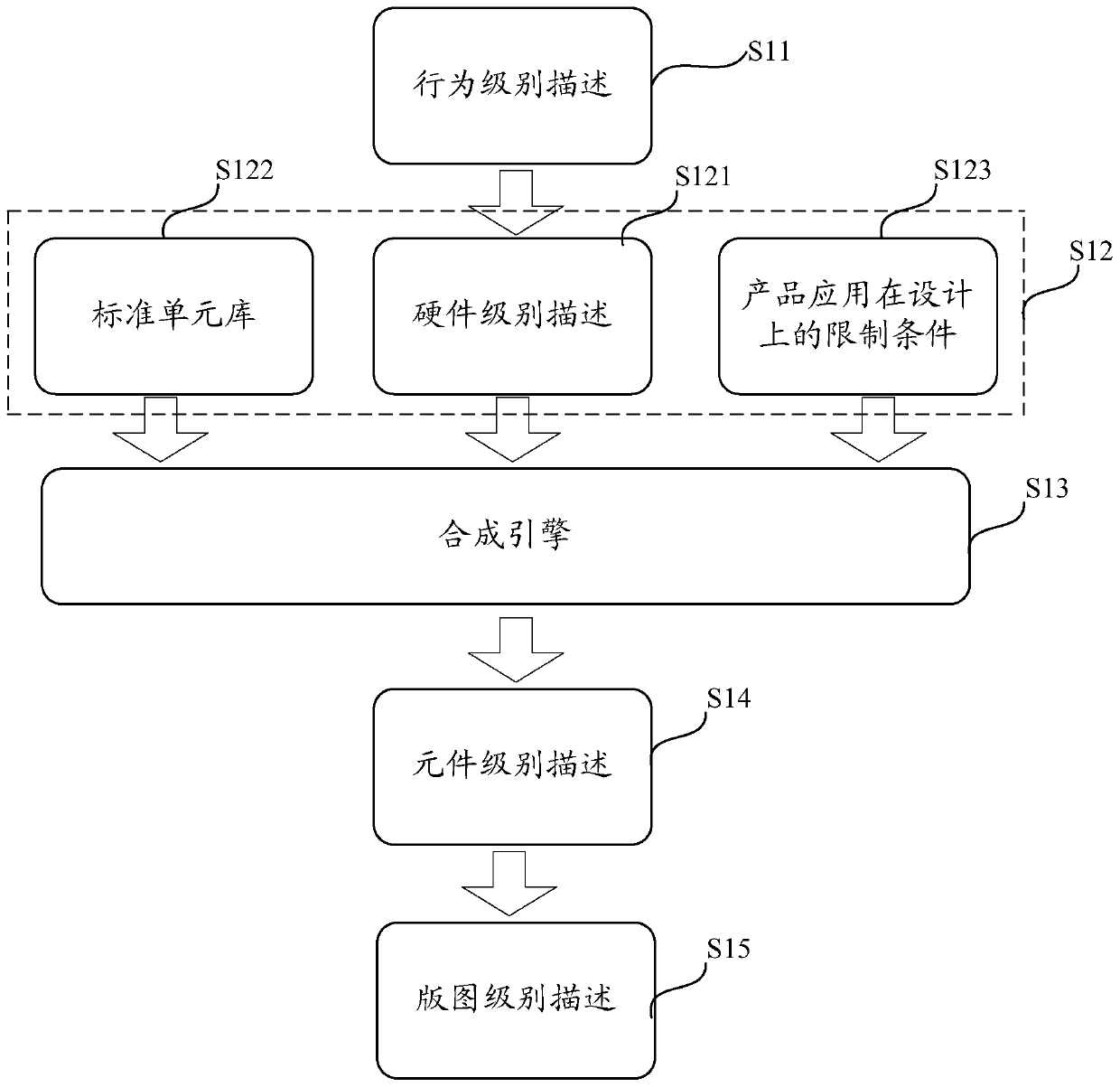

[0057] Please refer to figure 1 , a traditional chip design process includes the following steps:

[0058] S11, perform level description behavior level description to determine the function, performance and area of the chip to be designed;

[0059] S12, providing the required logic synthesis conditions, including: S121, performing hardware level description according to the behavior level description; S122, providing a standard cell library; S123, providing constraints representing the chip application environment (i.e. application requirements) (i.e. product application design constraints);

[0060] S13, perform logic synthesis, that is, according to the hardware level description, plus the restriction conditions, select a suitable standard cell from the standard cell library to generate a chip circuit;

[0061] S14, perform component-level description (i.e., gate-level description) on the chip circuit, that is, describe the connection relationship between gates in the c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com