Novel chip packaging body and packaging method thereof

A technology of chip packaging and packaging method, which is applied in the manufacturing of electric solid state devices, semiconductor devices, semiconductor/solid state devices, etc., can solve the problems of increasing the number of leads, high cost, increasing peripheral devices and direct observation of electrical damage, etc., to achieve the production process. Simple and flexible, the effect of avoiding external force damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

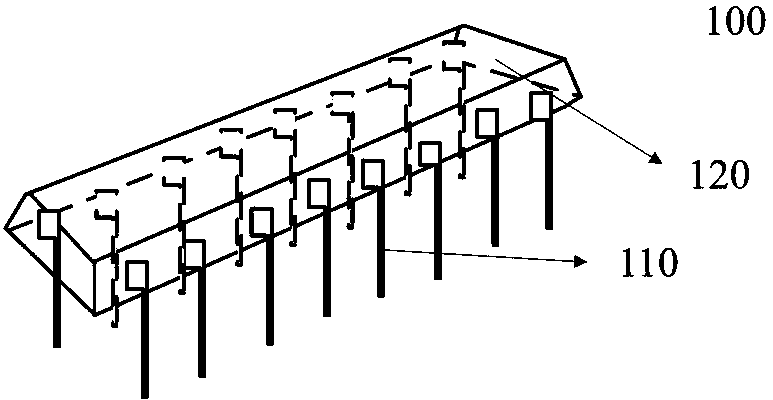

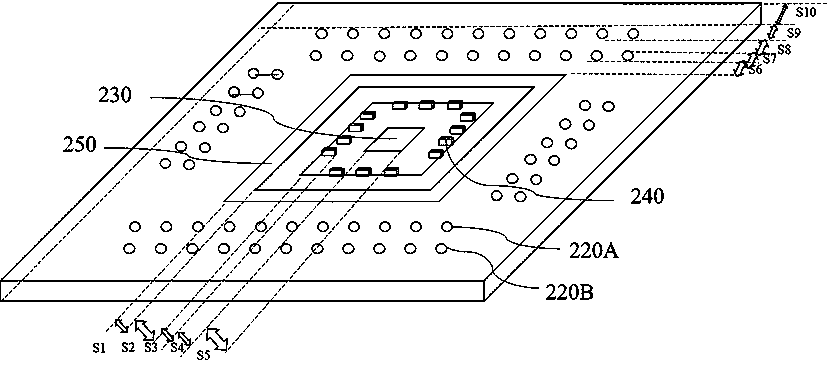

[0030] see figure 2 , a three-dimensional structure diagram of a novel chip package embodied in the present invention. The new chip package includes a base plate 200, pins 300 and a cap 400, wherein the base plate 200 includes a substrate 210, a through hole 220, a well bottom 230, a gold finger 240 and a base step 250; 210 is made of specific phenolic plastic with a thickness of 1.5 mm. There are several through holes 220 on each of the four sides of the substrate 210. The diameter of the through holes is 0.889 mm; the through holes 220 are divided into inner layer through holes 220A and outer layer through holes 220B. The through hole 220A and the outer layer through hole 220B are relatively parallel arranged, the hole spacing between the inner layer through hole 220A and the outer layer through hole 220B is 1.778mm, and the linear distance between the inner layer through hole 220A and the edge of the outer layer through hole 220B is 0.889mm mm, the inner layer through hol...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com