Two-dimensional material heterojunction back gate negative capacitance tunneling transistor and preparation method thereof

A two-dimensional material and heterojunction technology, which is applied in the field of two-dimensional material heterojunction back-gate negative capacitance tunneling transistor and its preparation, can solve the problem of low on-state current, reduce off-state current and increase on-state current , to solve the effect of low open current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

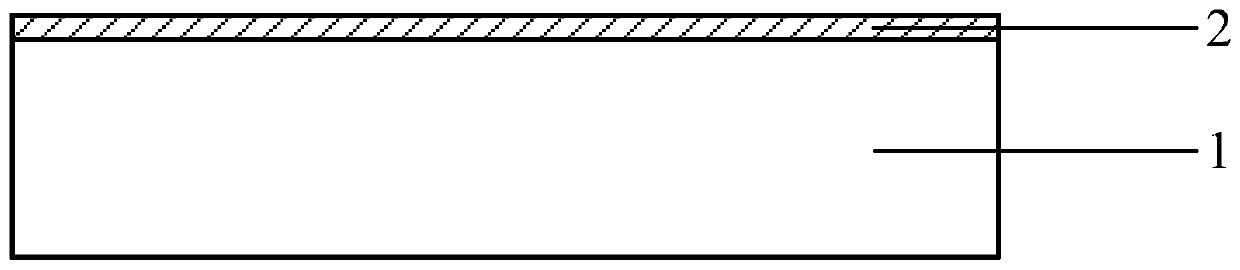

[0044] 2. Embodiment 1: refer to Figure 2 to Figure 9 , a method for preparing a two-dimensional material heterojunction back-gate negative capacitance tunneling transistor, comprising the following steps:

[0045] Step 1: Select a P-type Si substrate with a diameter of 2 inches and a crystal orientation of (100), and the doping concentration of the substrate is 1×10 18 / cm 3 , The resistivity is 0.1~0.5Ω·cm. In order to remove the natural oxides and impurities on the surface of the substrate, the substrate needs to be cleaned. The specific steps are as follows:

[0046] (1) Put the Si substrate into an acetone solution and ultrasonically clean it for 5 minutes, put the acetone-cleaned substrate into an ethanol solution and ultrasonically clean it for 5 minutes, and finally rinse it with deionized water for 1 minute to remove the Si substrate organic matter on the bottom;

[0047] (2) Clean the Si substrate in a mixed solution of hydrochloric acid, hydrogen peroxide, and ...

Embodiment 2

[0086] Embodiment 2: refer to Figure 2 to Figure 9 , a method for preparing a two-dimensional material heterojunction back-gate negative capacitance tunneling transistor, comprising the following steps:

[0087] Step 1: Select a P-type Si substrate with a diameter of 2 inches and a crystal orientation of (100), and the doping concentration of the substrate is 1×10 18 / cm 3 , The resistivity is 0.1~0.5Ω·cm. In order to remove the natural oxides and impurities on the surface of the substrate, the substrate needs to be cleaned. The specific steps are as follows:

[0088] (1) Put the Si substrate into an acetone solution and ultrasonically clean it for 5 minutes, put the acetone-cleaned substrate into an ethanol solution and ultrasonically clean it for 5 minutes, and finally rinse it with deionized water for 1 minute to remove the Si substrate organic matter on the bottom;

[0089] (2) Clean the Si substrate in a mixed solution of hydrochloric acid, hydrogen peroxide, and dei...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com