Method of preparing SOI silicon wafer by adopting rapid heat processing process

A rapid heat treatment, silicon wafer technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of high surface roughness of SOI, uneven temperature of silicon wafers, uneven film thickness, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

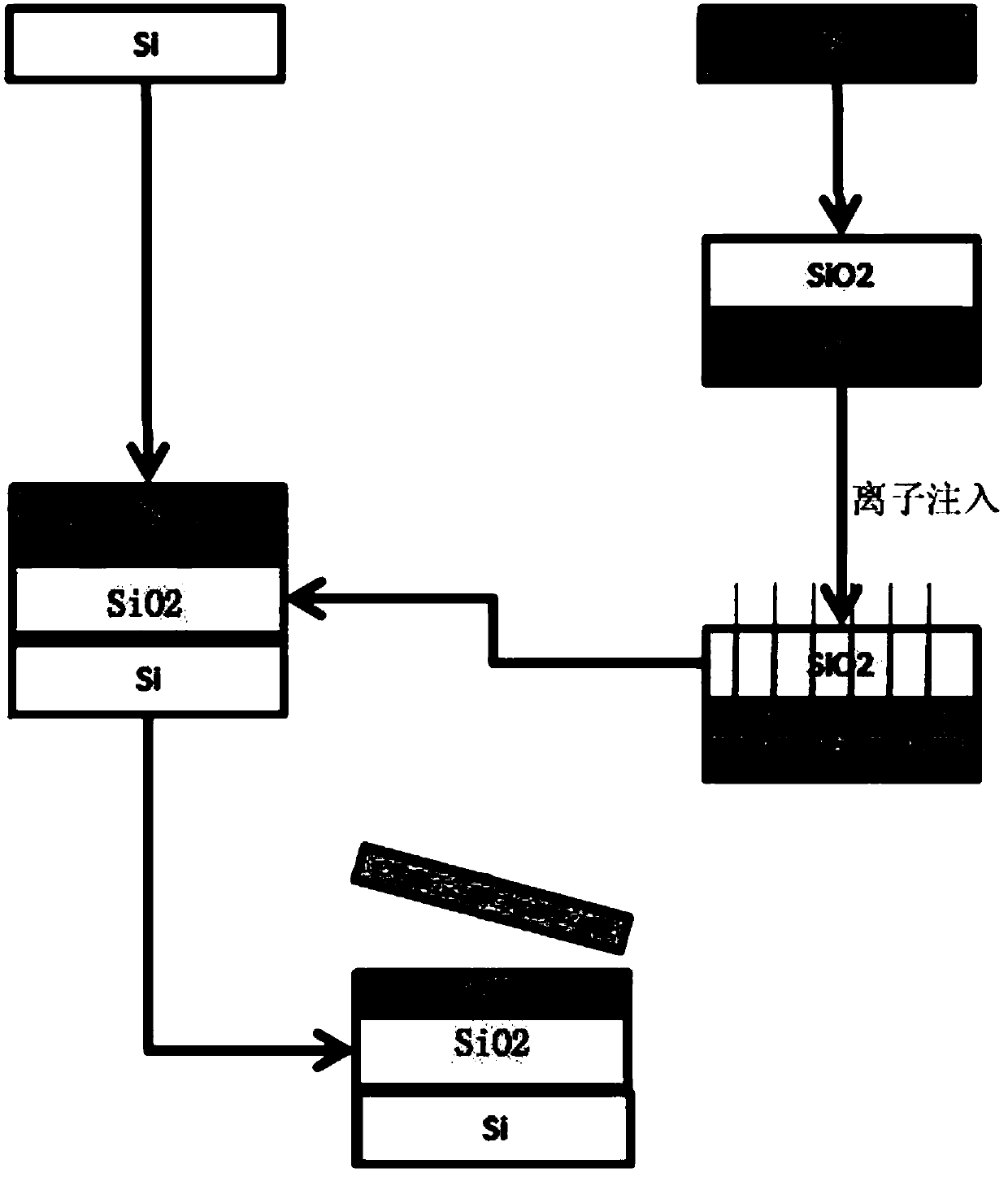

[0025] A method for preparing SOI silicon wafers by using a rapid heat treatment process, which meets the following requirements: it uses silicon wafers as raw materials, and sequentially oxidizes, injects H + and bonding process steps to obtain H + The bonding sheet of the injection layer is split, and then the bonding sheet is cracked by a rapid thermal treatment process (RTP) and a microwave, that is, the desired SOI silicon chip can be obtained.

[0026] The method for preparing SOI silicon wafers using a rapid thermal treatment process meets the following requirements: a rapid thermal treatment process (RTP) single-chip process is used in the splitting process, the temperature is raised to a required temperature not exceeding 480°C, and the temperature is stabilized for 30S-10min. The rate is 10-200°C / S; after or during the rapid thermal treatment (RTP) process, the microwave process is applied to the bonding sheet, and the microwave power range is required to be adjusted...

Embodiment 2

[0038] This embodiment is a method for preparing SOI silicon wafers using RTP plus microwave split technology, and its process flow is as follows figure 1 shown. In this method, silicon wafers are used as raw materials, which are sequentially oxidized and implanted with low doses of H + and bonding process steps to obtain H + The bonding sheet of the injection layer is processed by RTP and microwave split technology with specific process parameters to obtain the required SOI silicon wafer.

[0039] Example 1

[0040] 1. Take an 8-inch P-type silicon wafer, its crystal orientation can be or , and its resistivity can be selected from heavily doped to high resistance.

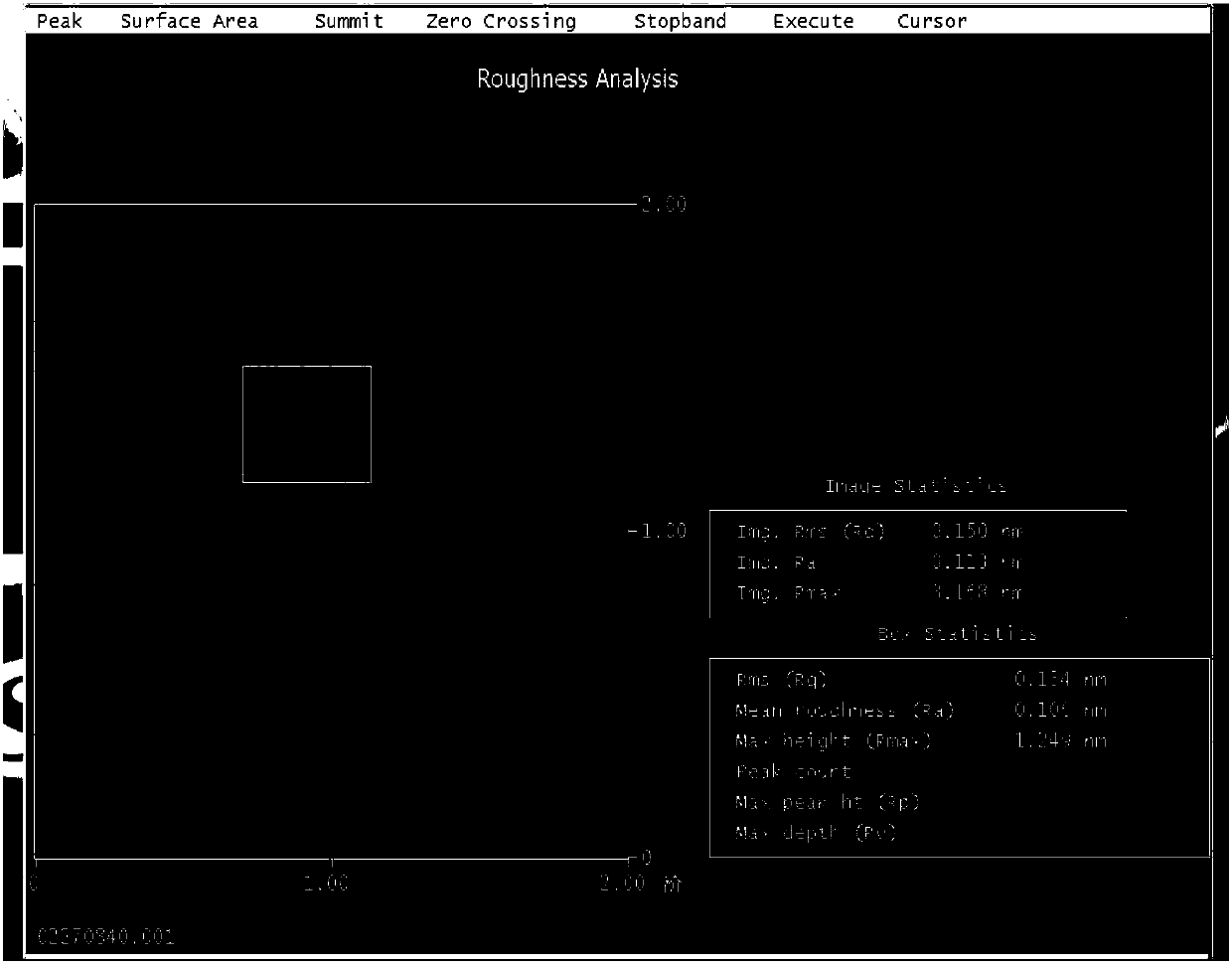

[0041]2. Prepare an oxide layer (silicon dioxide) on the silicon wafer: oxidize the surface of one side of the silicon wafer in step 1 (or both can be oxidized, according to actual process conditions), and obtain a silicon wafer with an oxide layer (Silicon dioxide is used as the BOX layer of SOI), the oxidat...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com