A charge storage type insulated gate bipolar transistor and a preparation method thereof

A bipolar transistor, charge storage technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., to achieve excellent device characteristics, improve concentration distribution, and change the band gap.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

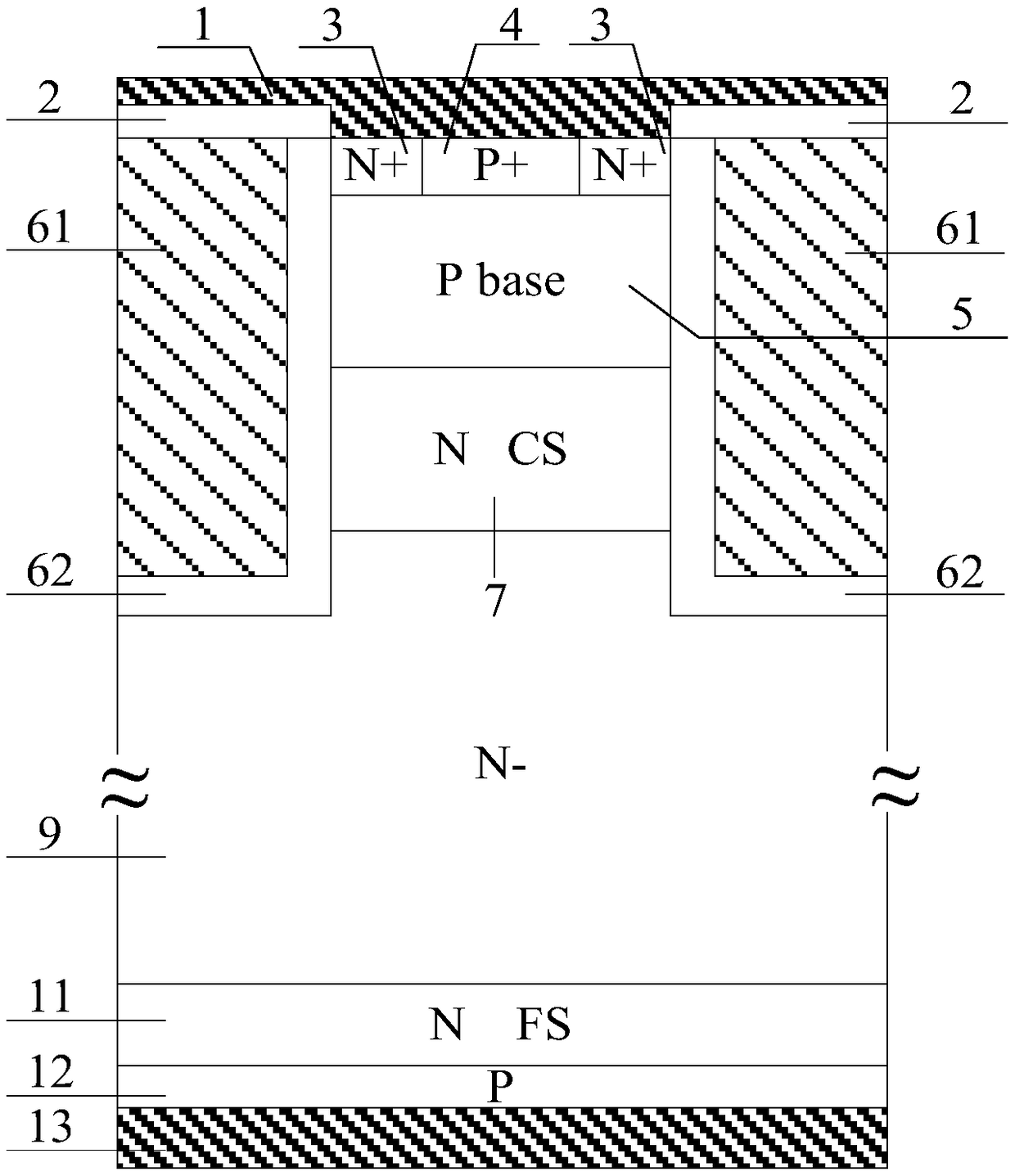

[0068] This embodiment provides a strained Si~Si 1-x Ge x Insulated gate bipolar transistor with homotype heterojunction charge storage layer, Figure 4 Its semi-cellular structure is shown, and its cellular structure includes: collector metal 13, P-type collector region 12, N-type field stop layer 11, N-drift region 9, N-type charge storage layer 7, P-type base Region 5, P+ emitter region 4, N+ emitter region 3, trench gate structure and emitter metal 1; collector metal 13 is arranged on the back of P-type collector region 12; N-type field stop layer 11 is arranged on P-type collector The front of the region 12; the N-type drift region 9 is arranged on the front of the N-type field stop layer 11; the P-type base region 5 is arranged on the top layer of the N-drift region 9; the P+ emitter region 4 is in contact with both sides of the P+ emitter region 4 The N+ emitter region 3 is arranged side by side on the top layer of the P-type base region 5; the N-type charge storage l...

Embodiment 2

[0075] This embodiment provides a strained Si~Si 1-x Ge x Insulated gate bipolar transistor with homotype heterojunction charge storage layer, Figure 11 Its semi-cellular structure is shown. In this embodiment, except that a P-type layer 10 with a junction depth of 0.5-1 μm is introduced at the bottom of the trench gate structure, other structures are the same as those in Embodiment 1.

[0076] This embodiment introduces a P-type layer 10 connected to the gate electrode 61 through a gate dielectric layer 62, and the P-type layer 10 extends laterally to both sides into the N-drift region 9 below the heterojunction N-type charge storage layer 7, so as to This shields the influence of negative charges in the N-type charge storage layer 7, improves the concentration of the electric field at the bottom of the trench, and improves the breakdown voltage and reliability of the device.

Embodiment 3

[0078] This embodiment provides a strained Si~Si 1-x Ge x Insulated gate bipolar transistor with homotype heterojunction charge storage layer, Figure 12 Its semi-cellular structure is shown. In this embodiment, except that the split electrode 81 and the split electrode dielectric layer 82 are introduced into the trench gate structure 6 to form the split trench gate structure, the rest of the structure is the same as that of the embodiment 2.

[0079] The depth of the gate electrode 61 in the split trench gate structure is greater than the junction depth of the P-type base region 5 and smaller than the junction depth of the N-type charge storage layer 7; the depth of the split electrode 82 is greater than the junction depth of the N-type charge storage layer 7 deep; the split electrode 82 is connected to the gate electrode 61 through the gate dielectric layer 62, and is connected to the N-type charge storage layer 7 and the N-drift region 9 through the split electrode dielec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com