A Shift-Based Instruction Fetching and Buffering Method and Superscalar Microprocessor

A technology of instruction extraction and buffering method, which is applied in the direction of concurrent instruction execution, electrical digital data processing, instruments, etc., can solve the problems such as the number of effective instructions is not fixed, the selection logic is complicated, and the extraction and buffering cannot be processed in a fixed way. Achieve the effect of reducing overhead, simple and easy logic, simple extraction logic and buffer logic

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

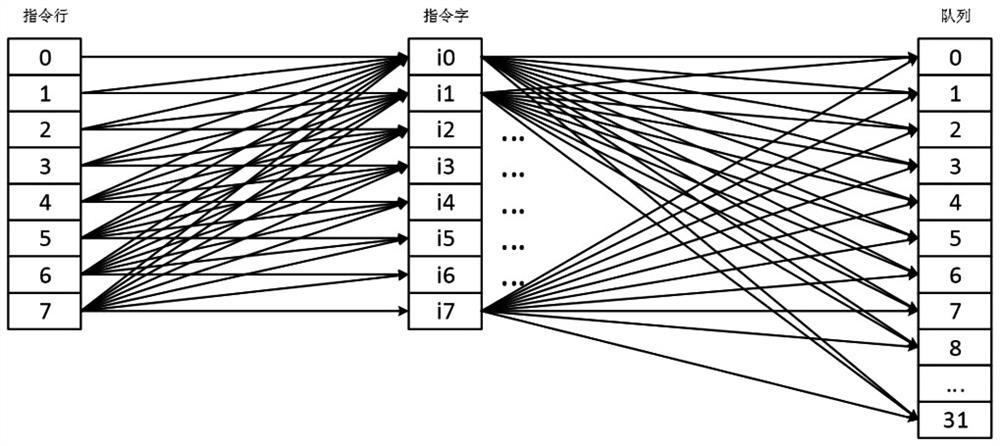

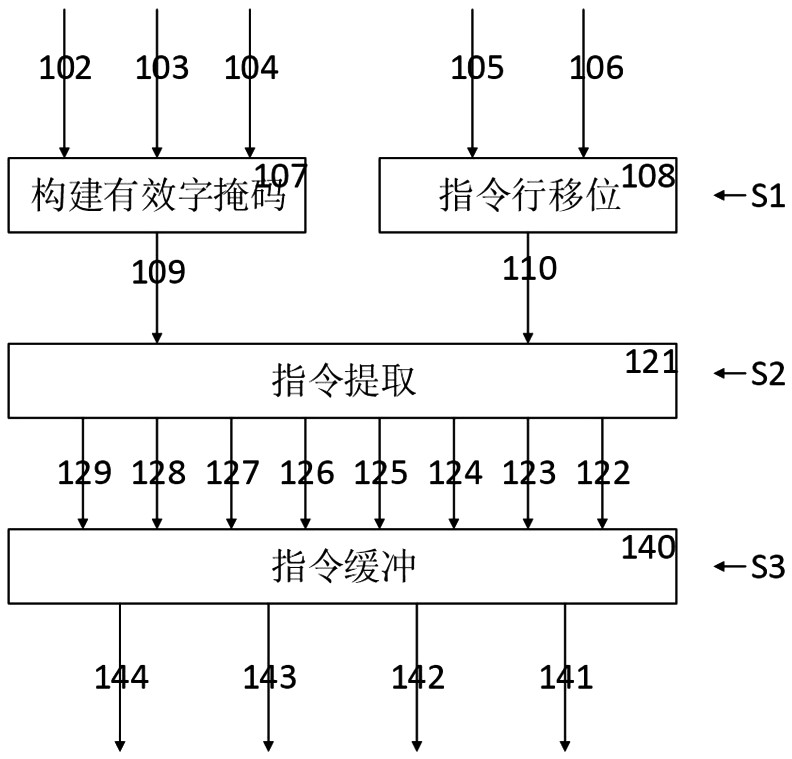

[0031] like figure 2 As shown, the implementation steps of the shift-based instruction fetching and buffering method in this embodiment include:

[0032] 1) Construct a valid word mask for the instruction word, if the mask is true, the instruction word is valid, otherwise, the instruction word is invalid;

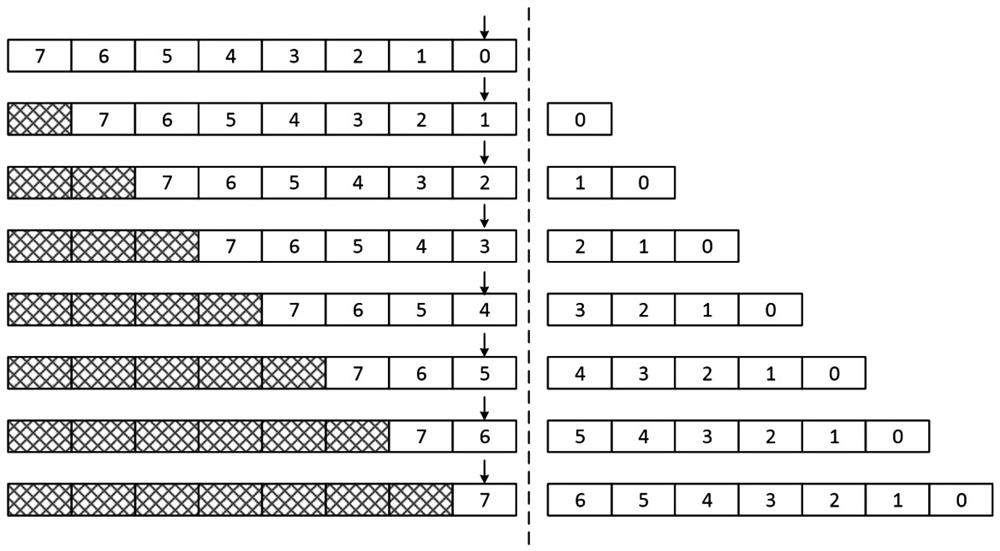

[0033] 2) Perform a right-aligned shift on the instruction line according to the instruction word offset;

[0034] 3) Split the shifted instruction line according to the word width according to the effective word mask and extract the effective word;

[0035] 4) Sort the valid words into the buffer block sequence;

[0036] 5) The buffer block sequence is written into the buffer queue controlled by the write enable of the buffer item.

[0037] The shift-based instruction extraction and buffering method of this embodiment constructs an effective word mask according to the prediction offset provided by the branch prediction information and the instruction word offset provid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com