Curable resin composition and fan out type wafer level package

A technology of curable resin and curable components, applied in the direction of electric solid devices, semiconductor/solid device parts, circuits, etc., to achieve the effect of reducing warpage and high quality and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

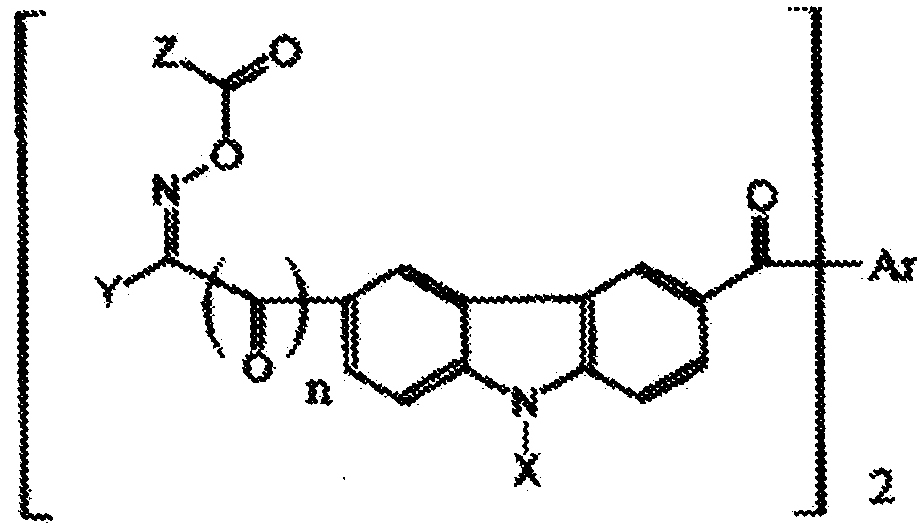

Method used

Image

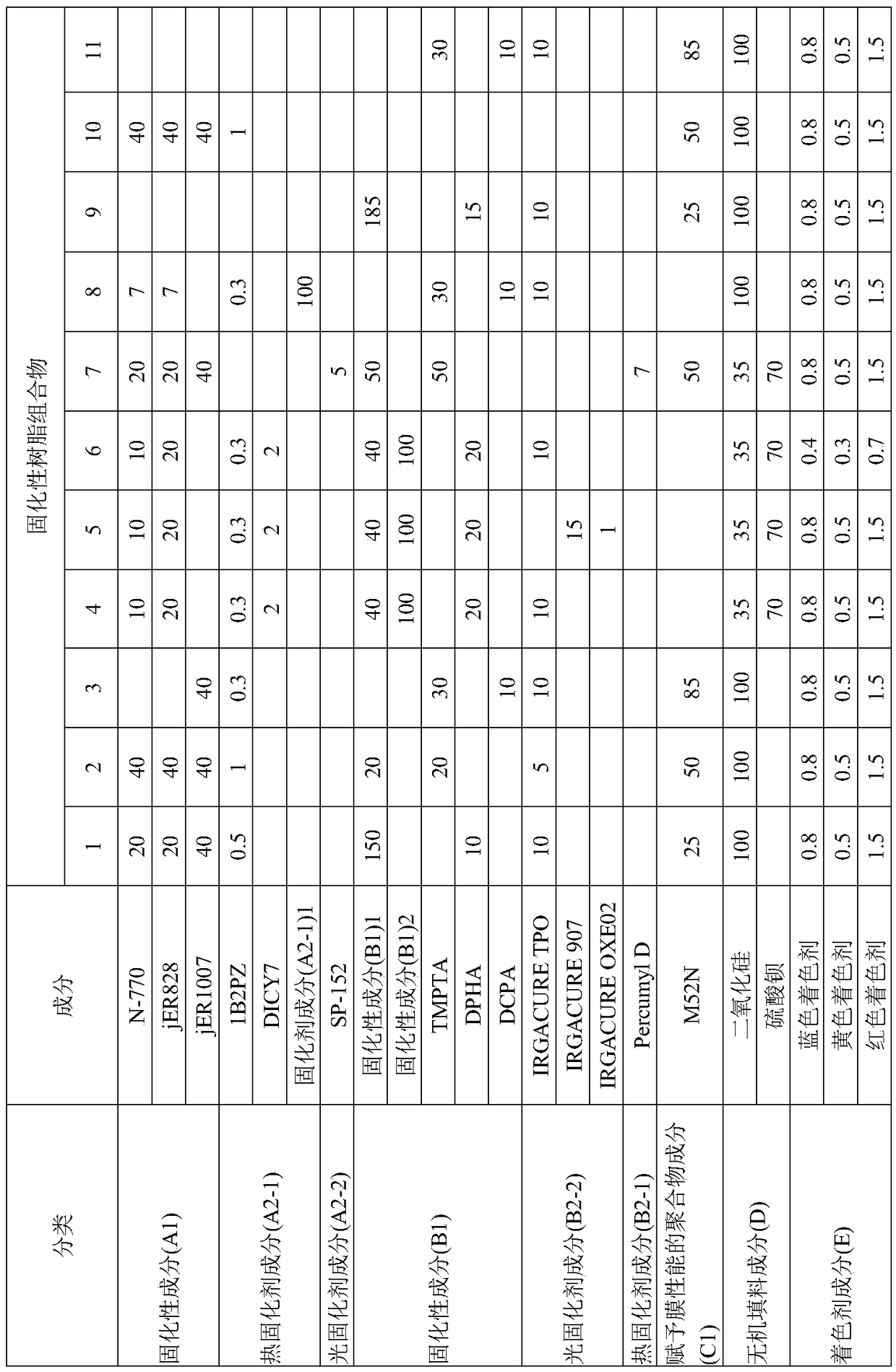

Examples

Embodiment

[0213] Hereinafter, the present invention will be described by way of examples, but the present invention is not limited by these examples. In addition, unless otherwise stated, "part" and "%" mean a mass part.

[0214]

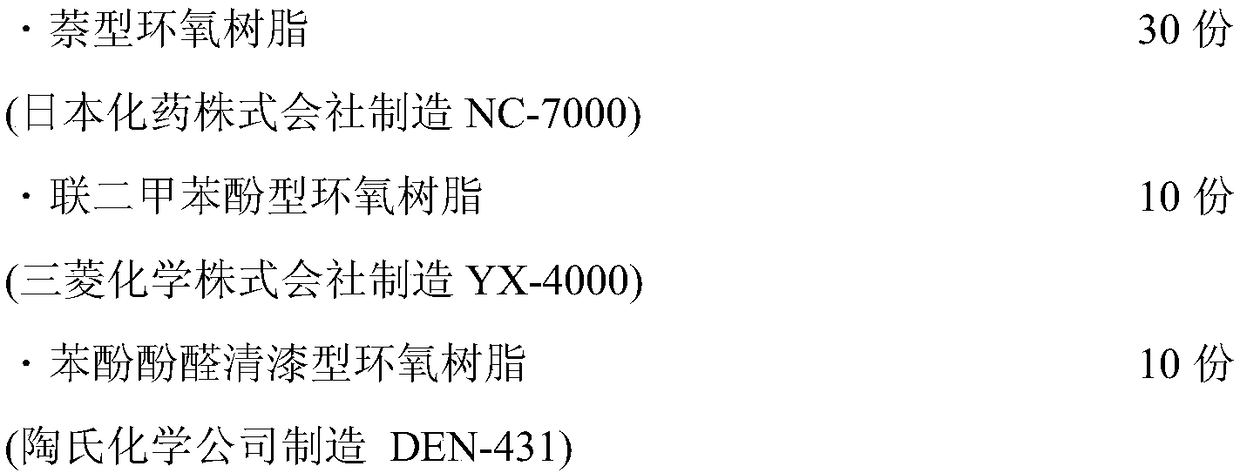

[0215] 119.4 parts of novolak-type cresol resin (manufactured by Showa Denko, Shonol CRG951, OH equivalent: 119.4) and 1.19 parts of potassium hydroxide were charged into an autoclave equipped with a thermometer, a nitrogen introduction device and an alkylene oxide introduction device, and a stirring device and 119.4 parts of toluene, nitrogen substitution was carried out in the system under stirring, and the temperature was raised by heating. Next, slowly add 63.8 parts of propylene oxide dropwise at 125°C to 132°C at a rate of 0 to 4.8kg / cm 2 React for 16 hours. After cooling to room temperature, 1.56 parts of 89% phosphoric acid was added and mixed to the reaction solution, and potassium hydroxide was neutralized to obtain a non-volatile component of 6...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Epoxy equivalent | aaaaa | aaaaa |

| Acid value | aaaaa | aaaaa |

| Solid content acid value | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com