A superjunction igbt device with mixed conduction modes

A device and mode technology, applied in the field of insulated gate bipolar transistors, can solve the problems of IGBT not being fully turned on, reliability problems, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

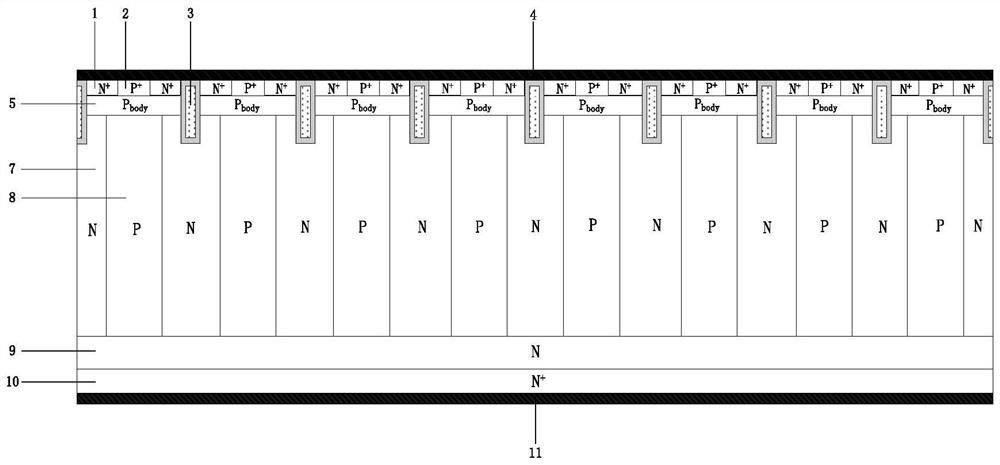

Embodiment 1

[0046] A superjunction IGBT device with a mixed conduction mode, comprising N+ collector regions 10 and P-type collector regions 12 arranged alternately, with N-type buffers on the upper surfaces of the N+ collector regions 10 and P-type collector regions 12 Layer 9, the upper surface of the N-type buffer layer 9 has a super junction drift region composed of a super junction N column region 7 and a super junction P column region 8, and the surface of the super junction drift region is composed of an N+ source region 1, a P+ A trench MOS structure consisting of a contact region 2, a polysilicon gate electrode 3, an emitter 4, and a Pbody base region 5 has a collector electrode 11 on the lower surface of the device, and between the N+ collector region 10 and the P-type collector region 12 There is a silicon dioxide layer 13 between them, the lower surface of the silicon dioxide layer 13 is in contact with the collector electrode 11, and the upper surface of the silicon dioxide la...

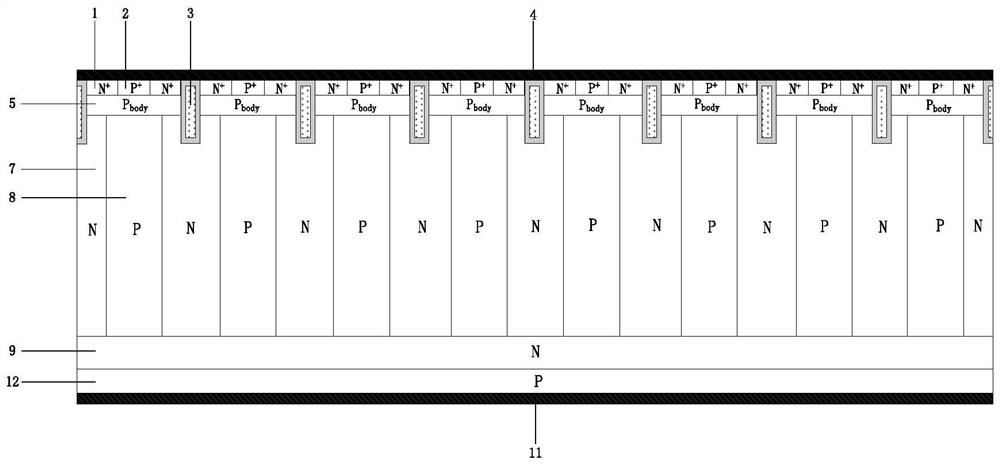

Embodiment 2

[0048] Such as Figure 5 As shown, the difference between this example and Example 1 is that the trench MOS structure is a planar gate structure.

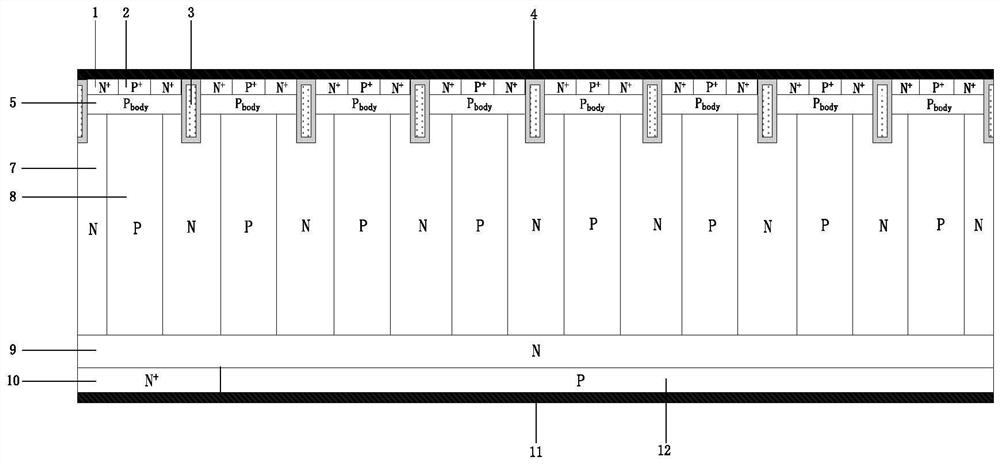

Embodiment 3

[0050] Such as Figure 6 As shown, the difference between this example and Example 1 is that there is an N-type carrier storage layer 6 between the superjunction drift region and the surface MOS structure Pbody base region 5, and the N-type carrier storage layer The concentration of 6 is not less than that of the superjunction N-column region 7. Compared with Embodiment 1, this embodiment can further reduce the turn-on voltage drop and improve the turn-off performance of the device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com