A method for manufacturing a multi-slot gate lateral high-voltage power device

A technology for power devices and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of slow device turn-off speed, device latch-up effect, and reduction of forward conduction voltage drop, etc. Achieve low turn-off loss, fast turn-off speed, and high compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0032] The manufacturing process of the multi-groove gate SOI LIGBT device in this example is as follows:

[0033] A method for manufacturing multi-groove gate SOI LIGBT, characterized in that it comprises the following steps:

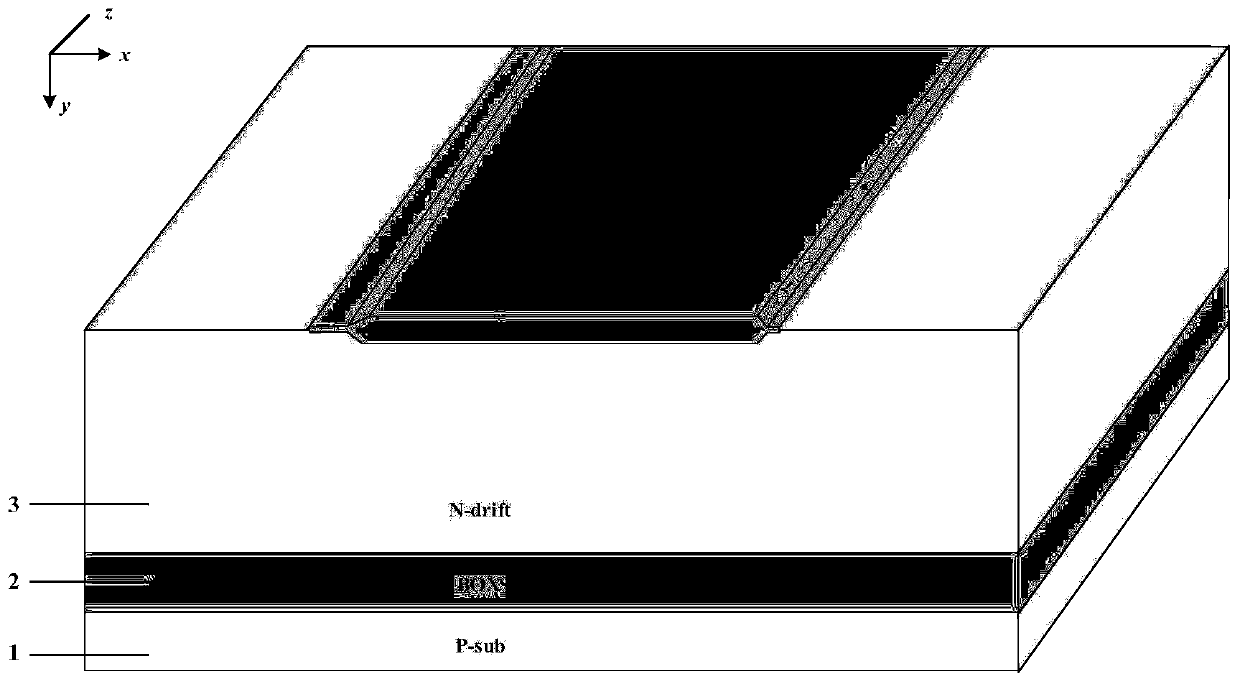

[0034] The first step: preparing SOI material, the SOI material includes bottom-up substrate layer 1, insulating dielectric layer 2 and N-type drift region 3, such as figure 1 shown;

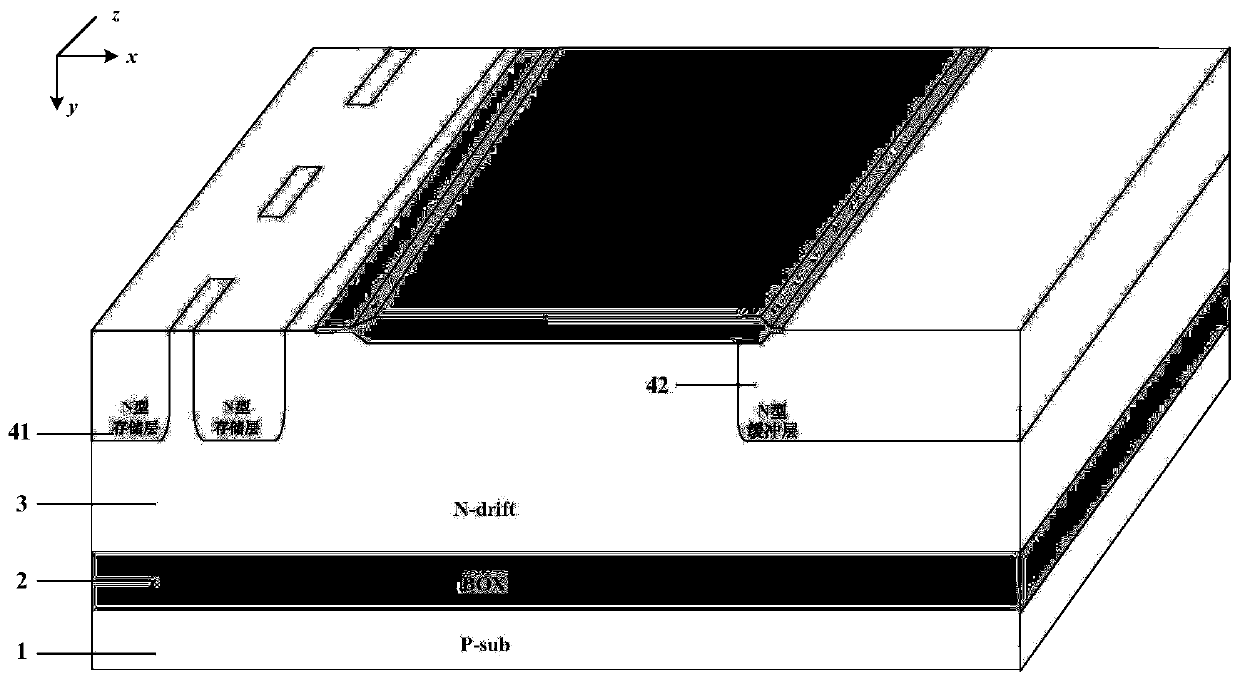

[0035] Step 2: Implanting N-type impurities into one end of the surface of the N-type drift region 3 through ion implantation technology, and the impurity implantation windows are distributed in segmented patterns;

[0036] Step 3: Implanting N-type impurities into the other end of the surface of the N-type drift region 3 by ion implantation technology;

[0037] The fourth step: the second step and the third step of the ion-implanted N-type impurity are simultaneously subjected to high-temperature push-in junction, correspondingly forming the N-type storage layer 41 at...

Embodiment 2

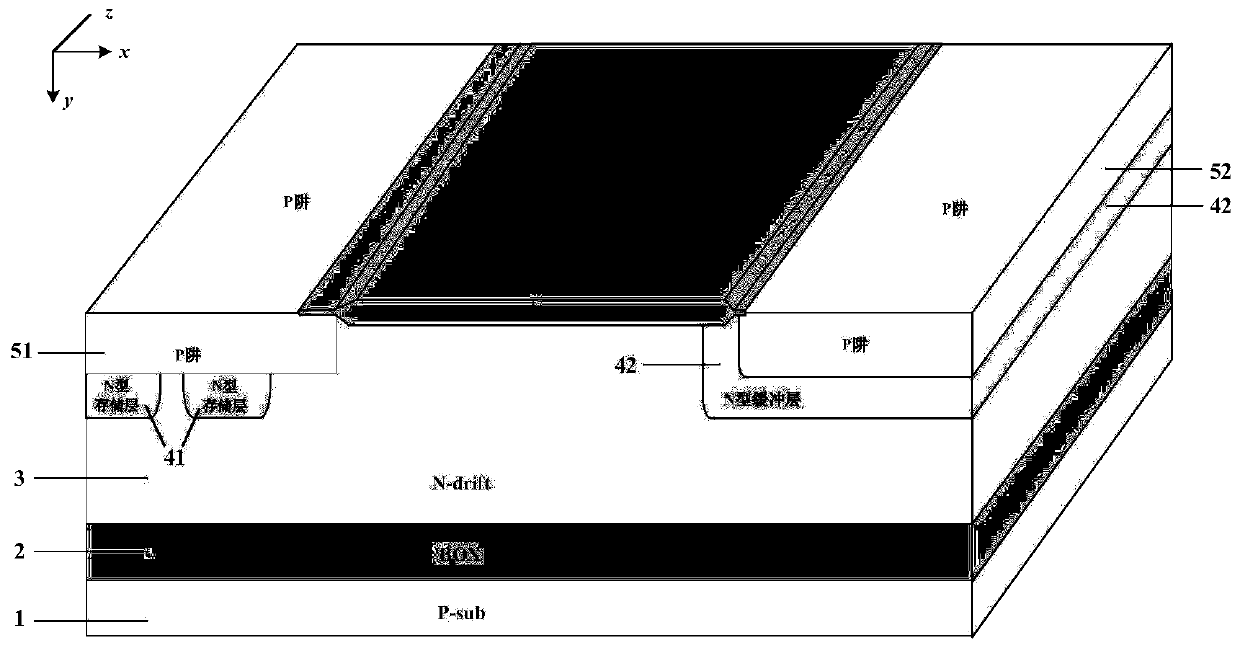

[0050] Such as Figure 8 Shown, in this example and embodiment 1 Figure 4 The difference is that in the eighth step of this example, the emitter end controls the bottom of the groove gate and the bottom of the blocking groove gate is implanted to form a P-type buried layer 53 . The working mechanism of device shutdown in this embodiment is consistent with that of Embodiment 1, the difference is that: when conducting forward conduction, the P-type buried layer 53 introduced in this example can assist in depleting the N-type storage layer 41, thereby improving the efficiency of the N-type storage layer. 41 Optimize the doping concentration and enhance the carrier storage effect, so in this example, the carrier concentration in the drift region of the device is higher, and the conduction voltage drop can be further reduced; at the same time, in the blocking state, the P-type buried layer 53 can also The electric field peak at the bottom of the emitter groove gate structure is r...

Embodiment 3

[0052] Such as Figure 9 and Figure 10 Shown, in this example and embodiment 1 Figure 7 The difference is that the layout of the emitter control grid and the collector grid can be intermittently distributed in rectangles or hexagons; Figure 11 It is shown that the emitter control slots and the collector slots are interconnected in a rectangular layout, of course, the emitter control slots and the collector slots may also be interconnected in a hexagonal layout. The device turn-off working mechanism in this embodiment is the same as that in Embodiment 1, the difference is that the shape of the groove gate can change the channel density of the device, which is beneficial to design the turn-on voltage drop and turn-off loss of the device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com