A shielded gate vdmos device with limited avalanche breakdown point

An avalanche breakdown and shielded gate technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as reducing parasitic BJT base resistance, increasing the threshold voltage of DMOS devices, and unable to completely prevent parasitic BJT transistors from turning on. The effect of improving withstand voltage and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

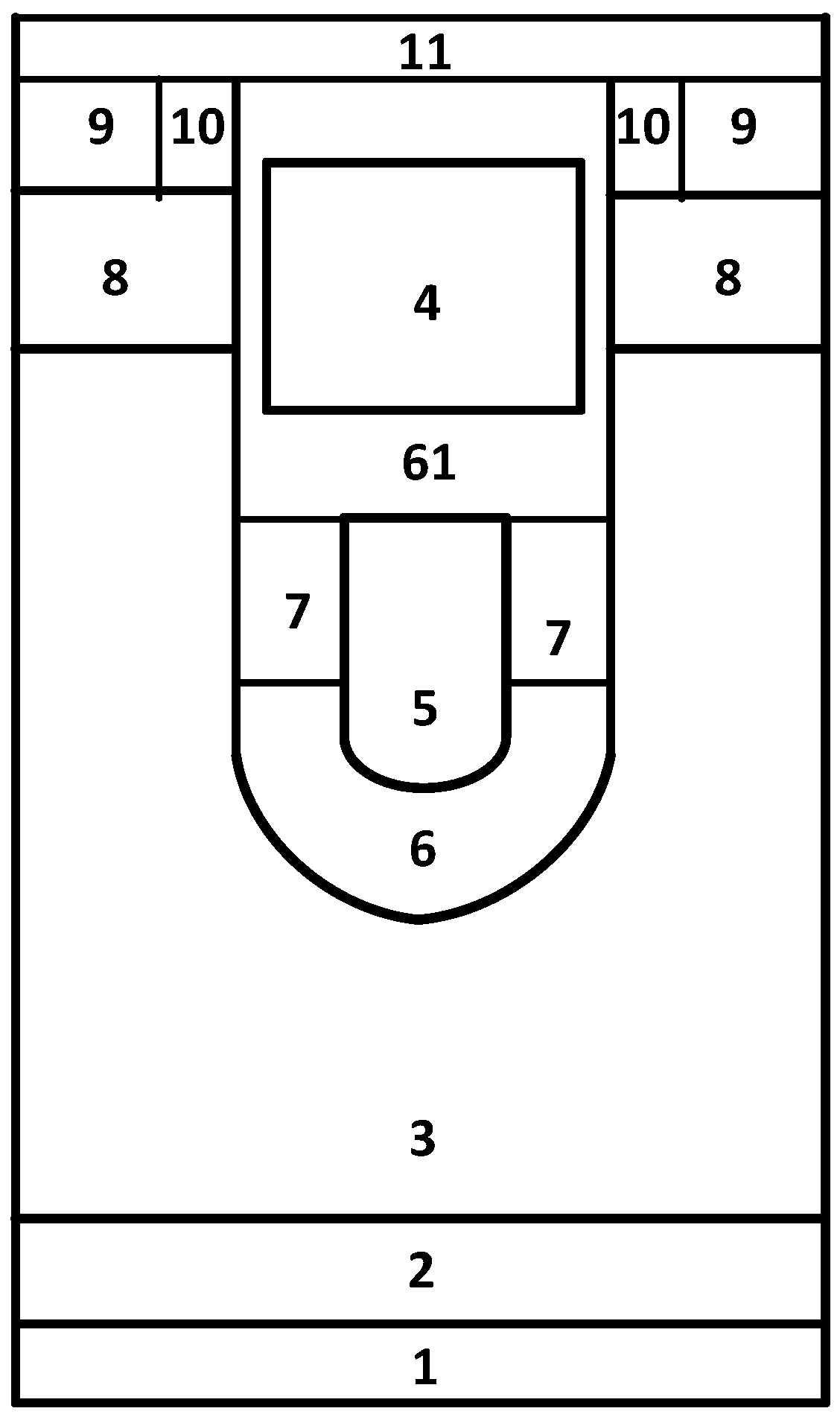

[0019] A shielded gate VDMOS device with a defined avalanche breakdown point, such as figure 1 As shown, it includes a metallized drain 1, a first conductive type semiconductor doped substrate 2, a first conductive type semiconductor doped drift region 3 and a metallized source 11 that are stacked sequentially from bottom to top; Type semiconductor doped drift region 3 has a groove gate, the second conductivity type semiconductor body region 8 is located on both sides of the groove gate and is in direct contact with the groove gate; the upper part of the second conductivity type semiconductor body region 8 has a second conductivity type semiconductor The doping contact region 9 and the first conductivity type semiconductor doping source region 10; the upper surface of the first conductivity type semiconductor doping source region 10 is in contact with the metallized source 11; the second conductivity type semiconductor doping contact The upper surface of the region 9 is in con...

Embodiment 2

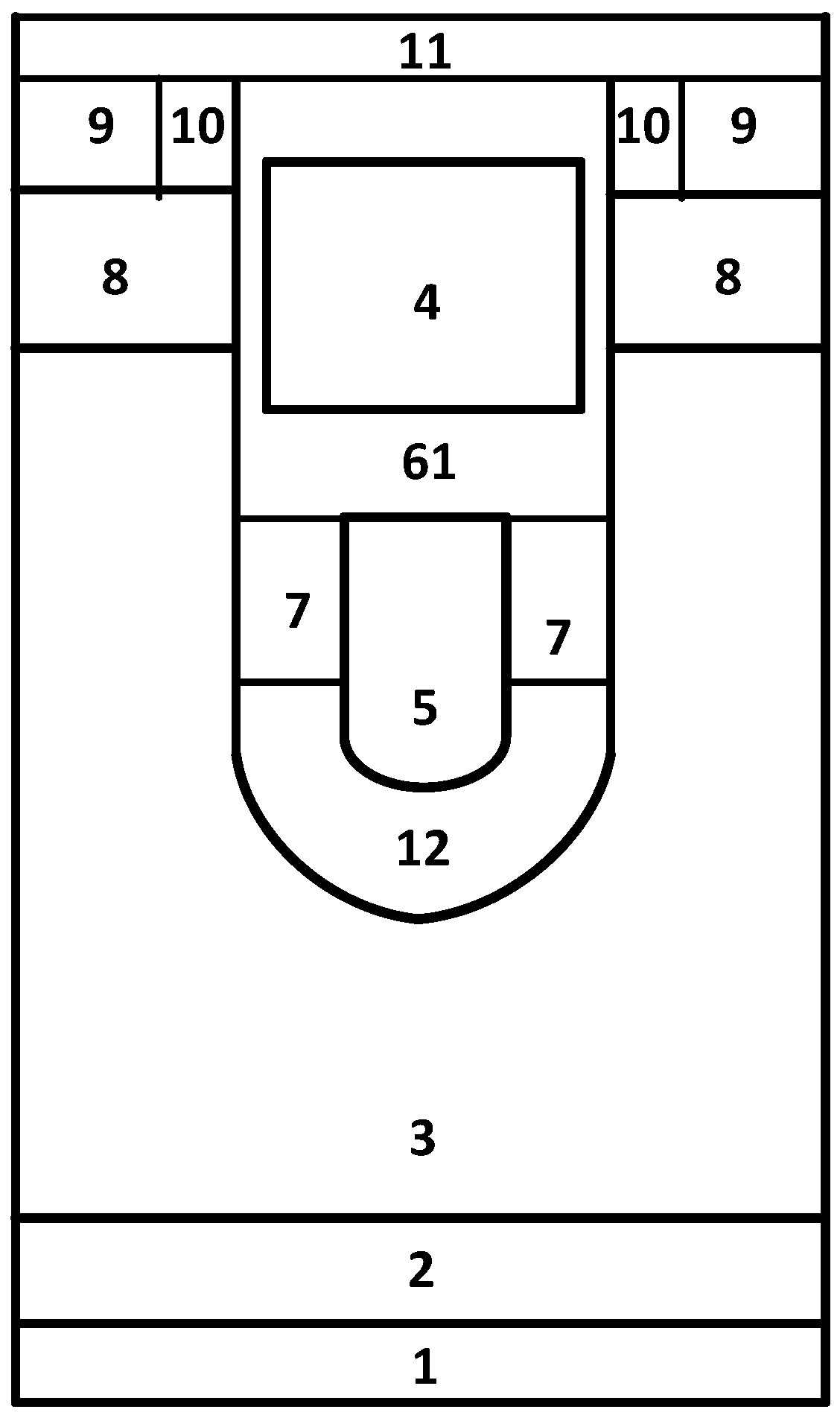

[0025] Such as image 3 As shown, the structure of this example is based on Example 1, the first dielectric layer 6 is replaced by a fourth dielectric layer 12, and the fourth dielectric layer 12 is made of a low-K dielectric material. That is, the dielectric constant of the material used in the second dielectric layer 7 is greater than that of the material used in the third dielectric layer 61, and the dielectric constant of the material used in the third dielectric layer 61 is greater than that of the material used in the fourth dielectric layer 12. The dielectric constant of the material. A low-K dielectric layer is used at the bottom of the trench gate, which can further improve the withstand voltage of the device.

Embodiment 3

[0027] Such as Figure 4 As shown, the structure of this example is based on Embodiment 1, the first dielectric layer 6 is replaced by a fourth dielectric layer 12, and the fourth dielectric layer 12 is made of a low-K dielectric material; the third dielectric layer 61 The fifth dielectric layer 13 is used instead, and the fifth dielectric layer 13 is made of a high-K dielectric material with a lower dielectric constant than the second dielectric layer 7 . That is, the dielectric constant of the material used in the second dielectric layer 7 is greater than the dielectric constant of the material used in the fifth dielectric layer 13, and the dielectric constant of the material used in the fifth dielectric layer 13 is greater than that of the material used in the fourth dielectric layer 12. the dielectric constant. A low-K dielectric layer is used at the bottom of the trench gate, which can further improve the withstand voltage of the device. The control gate electrode 4 is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com