Chip packaging structure and method

A chip packaging structure and packaging layer technology, which is applied to electrical components, electrical solid devices, circuits, etc., can solve the problems of low chip packaging space utilization and single circuit function

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

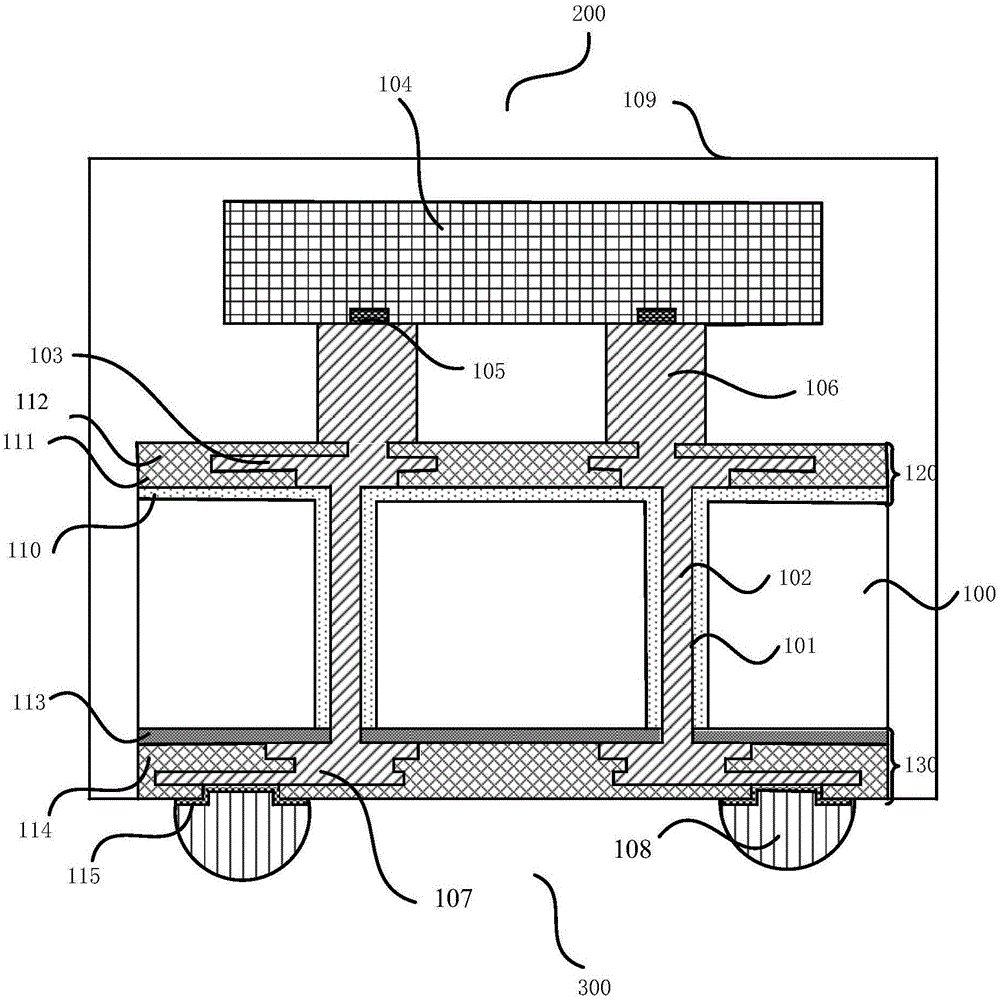

[0041] figure 1 It is a schematic diagram of a chip package structure provided by an embodiment of the present invention. This embodiment is applicable to various chip packaging situations, and is applied to high-end chips, such as Field Programmable Gate Array (Field Programmable Gate Array, FPGA), Graphics Processing Unit (Graphics Processing Unit, GPU), Central Processing Unit (Central Processing Unit , CPU) and high bandwidth memory (High Bandwidth Memory, HBM), etc. A chip packaging structure provided by an embodiment of the present invention includes:

[0042] Base substrate 100, first side 200, second side 300, first redistribution layer 120, second redistribution layer 130, via hole 101, first conductive pillar 102, first redistribution sublayer 103, flip chip 104, electrode 105, second conductive pillar 106, second rewiring sublayer 107, first external connection bump 108, encapsulation layer 109, first insulating layer 110, first passivation layer 112, second diffu...

Embodiment 2

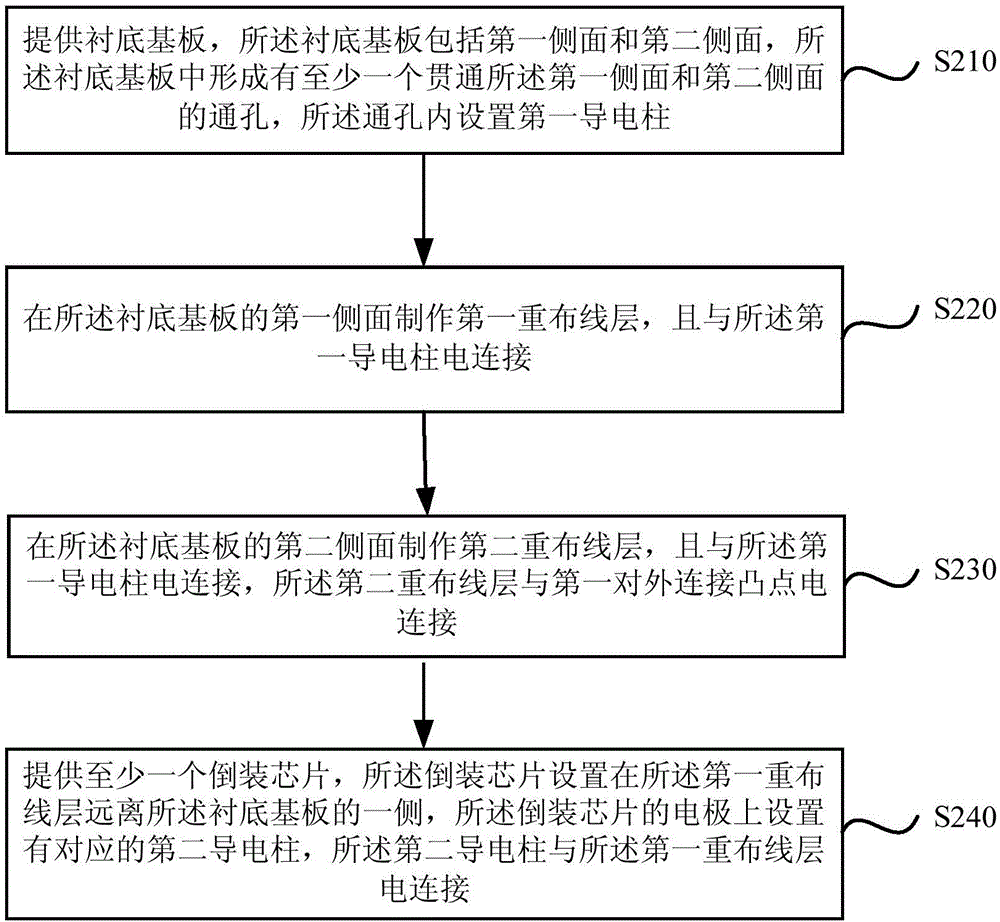

[0056] figure 2 The embodiment of the present invention also provides a flow chart of a chip packaging method, such as figure 2 Shown:

[0057] S210. Provide a base substrate, the base substrate includes a first side and a second side, at least one through hole penetrating through the first side and the second side is formed in the base substrate, and the through hole setting the first conductive column;

[0058] S220. Prepare a first redistribution layer on the first side surface of the base substrate, and electrically connect to the first conductive column;

[0059] S230. Prepare a second redistribution layer on the second side surface of the base substrate, and electrically connect to the first conductive column, and the second redistribution layer is electrically connected to the first external connection bump;

[0060] S240. Provide at least one flip chip, the flip chip is arranged on the side of the first redistribution layer away from the base substrate, and the el...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com