Doping silylene based MEMS piezoresistive pressure sensor and manufacturing method thereof

A pressure sensor, piezoresistive technology, applied in the measurement of fluid pressure by changing ohmic resistance, and the measurement of the property force of piezoresistive materials. problems such as limited sensitivity, to achieve the effect of good compatibility, high sensitivity, and simple manufacturing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

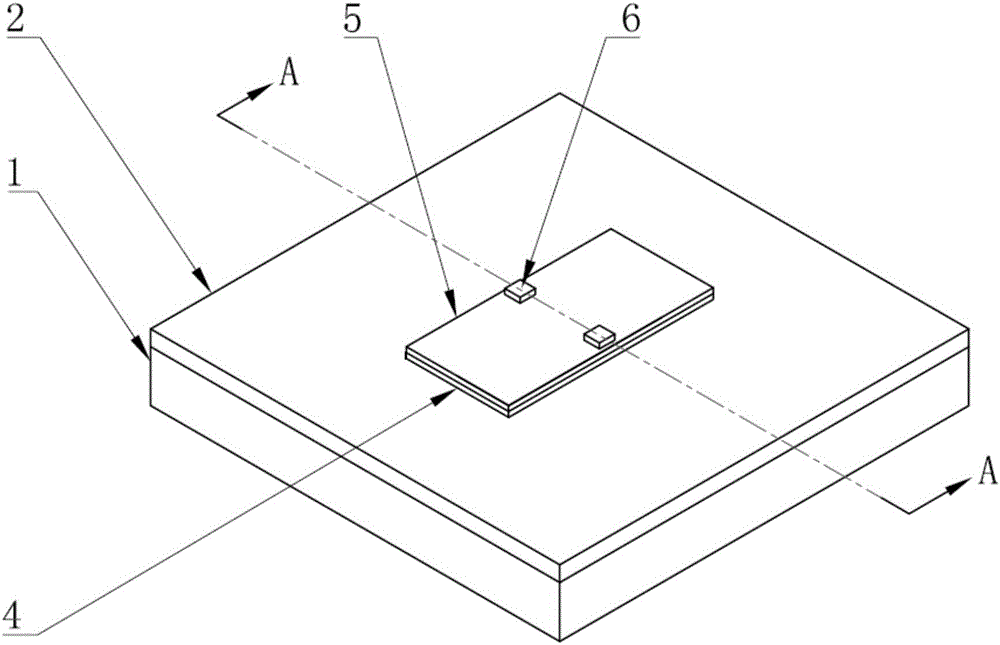

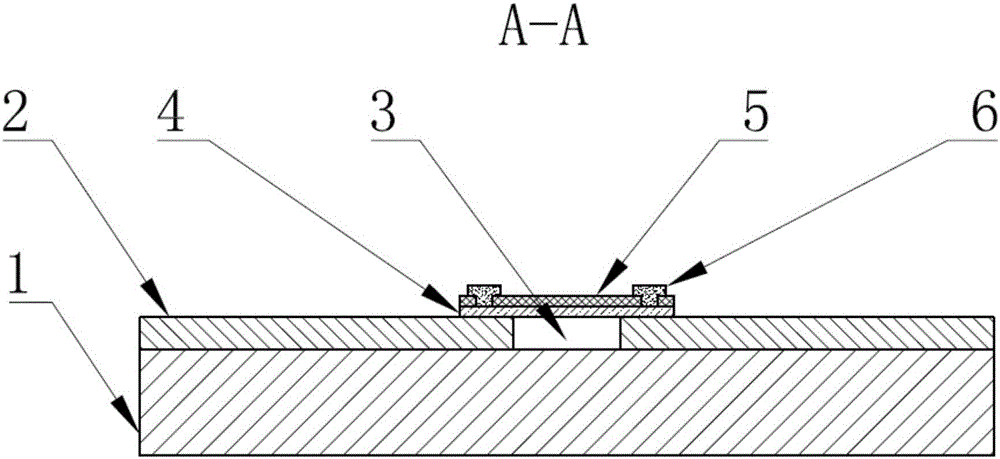

[0043] A manufacturing method of the first embodiment of the present invention comprises the following steps:

[0044] (1) After cleaning and drying a 300 μm thick silicon wafer as the substrate 1, deposit SiO with a thickness of 300 nm on its surface 2 insulating layer 2, and then cutting the silicon wafer into square pieces of 12mm×12mm;

[0045] (2) Reaction-coupled plasma (ICP) etching is performed on the insulating layer 2 to form a rectangular cavity 3, the depth of the cavity 3 is equal to the thickness of the insulating layer 2;

[0046] (3) Carry out sputter cleaning to Ag plate (cleaning condition is 600eV, Ar + ion, 10 -2 mT), annealed at 400°C to form a sharp P(1╳1), in ultra-high vacuum 10 -9 Epitaxial deposition of silicene at mT and substrate temperature of 250°C to form Ag-silicene layer;

[0047] (4) Invert the Ag-silicene layer so that the silicene faces down, and transfer the silicene face to the cavity 3 containing SiO 2 On the substrate 1 of the insulat...

no. 2 example

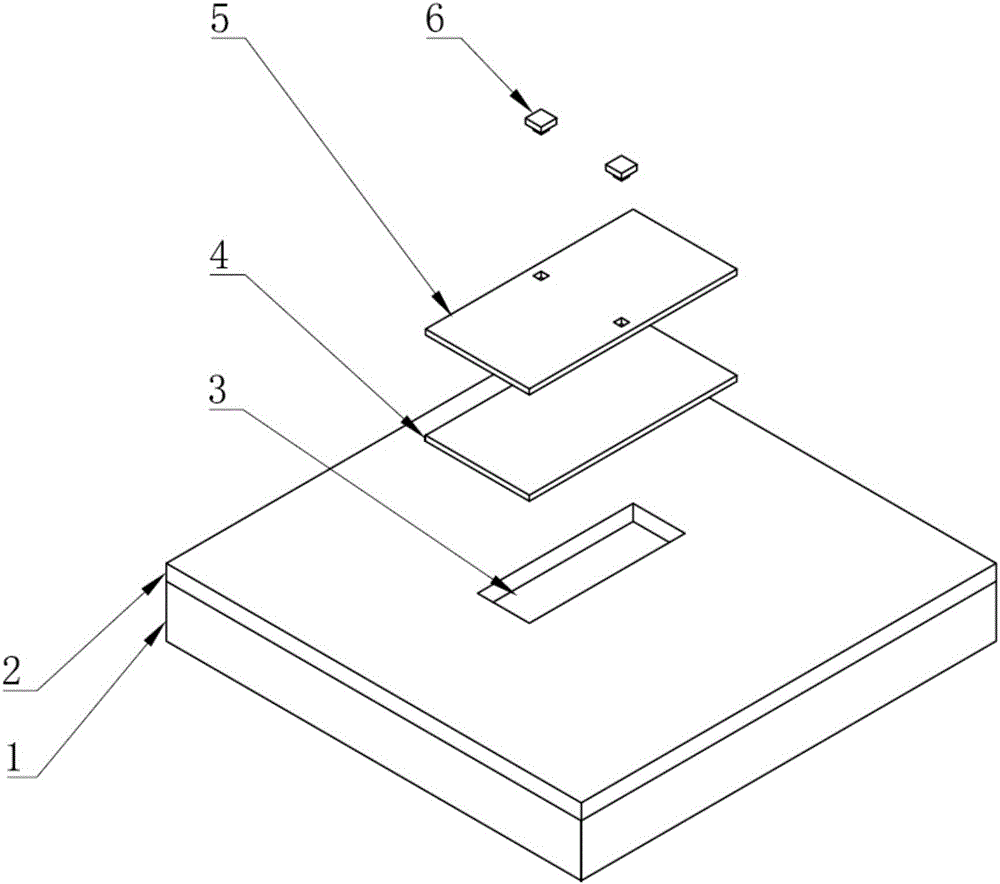

[0055] The manufacturing method of the second embodiment includes the following steps:

[0056] (1) Wash and dry a 300 μm thick wafer silicon (111) sheet as substrate 1, and deposit a layer of 1 μm thick β-Si on the upper surface 3 N 4 (0001) as insulating layer 2;

[0057] (2) Perform photolithography on the lower surface of the wafer silicon (111), and use ICP etching to obtain the cavity 3;

[0058] (3) In β-Si 3 N 4 (0001) surface carries out MBE deposition silicene thin film 4, and on described silicene thin film 4, forms a layer of 10nm thick SiO with LPCVD deposition 2 An anti-oxidation protective layer 5, followed by doping the silicene film 4;

[0059] (4) In the SiO 2 The surface of the anti-oxidation protection layer 5 corresponds to the position of the cavity 3, and two metal electrode patterns are obtained by photolithography, and 20 nm of Ti and 200 nm of Au are successively deposited on the two metal electrode patterns to form two metal electrodes 6 , the...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com