Method for improving profile of side wall of grid electrode, and semiconductor device manufacturing method

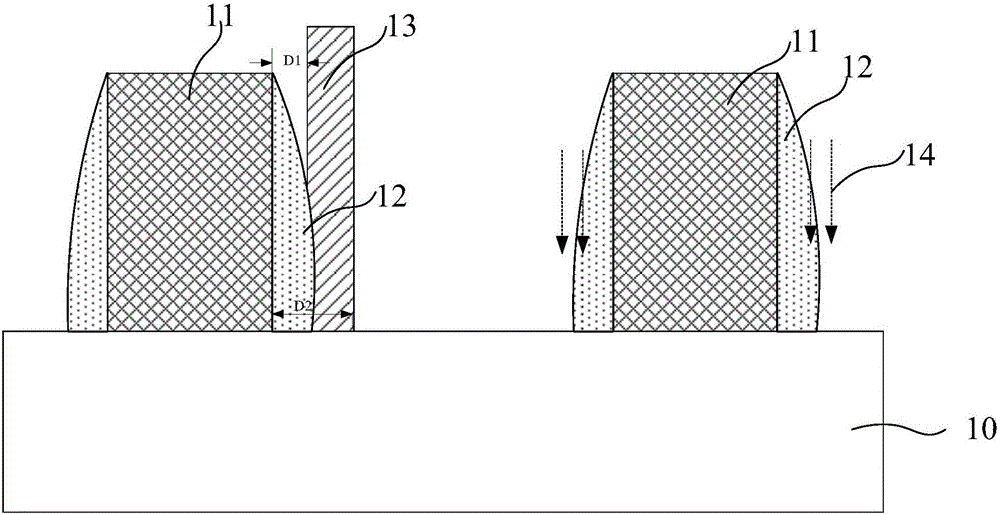

A gate sidewall and semiconductor technology, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve problems such as inability to insulate the gate from the contact hole 13, deterioration of device performance, and affect the quality of the device, so as to achieve an improvement threshold Voltage and leakage current issues, improving device performance, and reducing etching loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

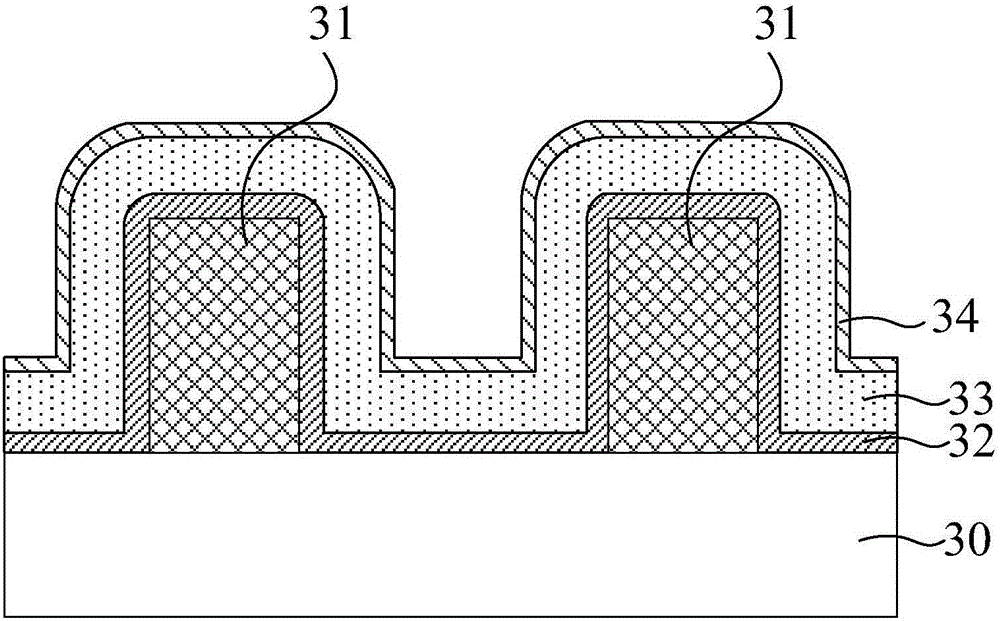

[0031] In order to make the purpose and features of the present invention more comprehensible, the specific embodiments of the present invention will be further described below with reference to the accompanying drawings. However, the present invention can be implemented in different forms and should not be limited to the described embodiments.

[0032] Please refer to figure 2 , This embodiment provides a method for improving the topography of the sidewall of the gate, including:

[0033] S1, forming a gate structure on the surface of a semiconductor substrate;

[0034] S2, forming a pad oxide layer, a sidewall layer for making sidewalls, and a protective layer for protecting the sidewalls in sequence on the surface of the semiconductor substrate and the gate structure, the thickness of the protection layer is smaller than that of the sidewalls Floor;

[0035] S3, using the sidewall layer as an etch stop layer, and etch through the protective layer to retain the protective layer on ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com