Method of forming semiconductor structure

A semiconductor and transistor technology, which is applied in the field of semiconductor structure formation, can solve the problems of metal interconnect structure resistance drift, increase of parasitic capacitance of metal interconnect structure, and reduce electrical performance of semiconductor devices, so as to optimize device electrical performance and increase bottom area, the effect of increasing the effective contact area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

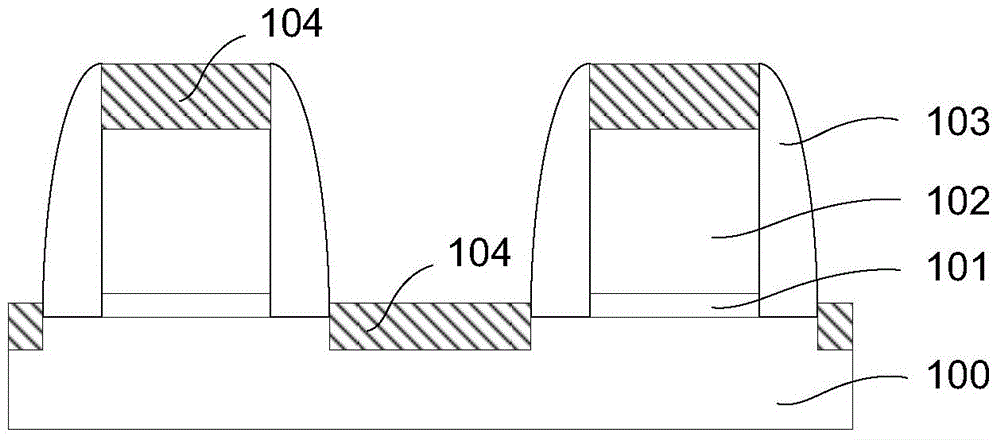

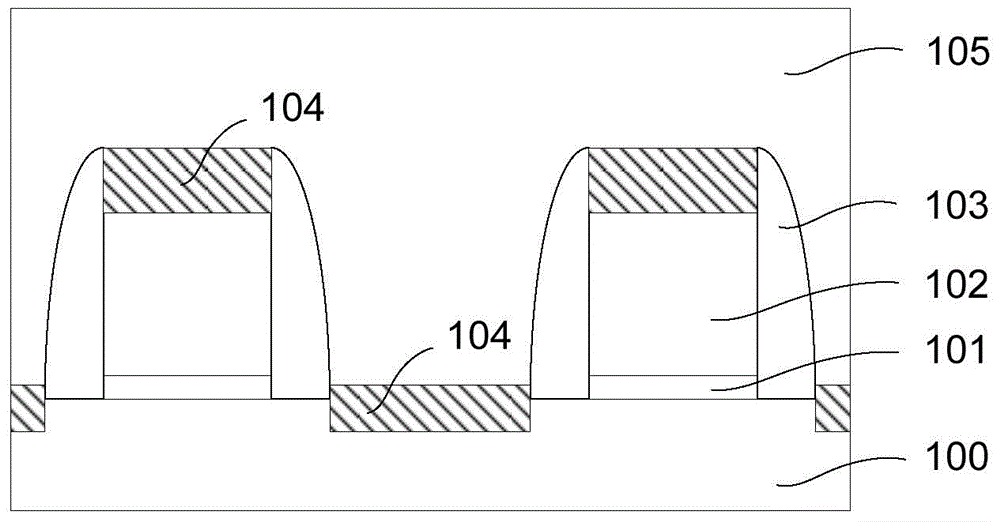

[0030] It can be seen from the background technology that with the continuous reduction of semiconductor feature size, the metal interconnection structure needs to perform high-performance and high-density connections in multi-layer and complex wiring layers, which brings great challenges to the manufacturing process of the metal interconnection structure. Not a small challenge, there are problems of resistance value drift and parasitic capacitance increase, which reduces the electrical performance of the device.

[0031] The research on the metal interconnection structure and its manufacturing process in the prior art found that: when forming the trench for filling the metal to obtain the wiring layer, the existing dry etching process is easy under the smaller mask opening. The cross-sectional shape of the groove with a relatively inclined side wall is formed. The groove shape will cause a serious reduction in the size of the bottom of the wiring layer, resulting in a decrease...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com