Formation method of semiconductor structure

A semiconductor and gate structure technology, which is applied in the field of semiconductor structure formation, can solve the problems such as the performance of MOS transistors needs to be improved, and achieve the effects of preventing bridging phenomenon, increasing the window, and improving integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

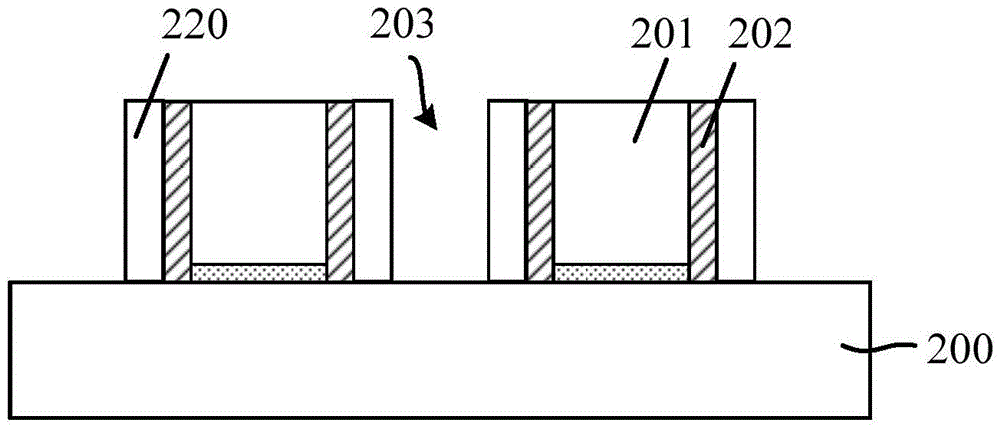

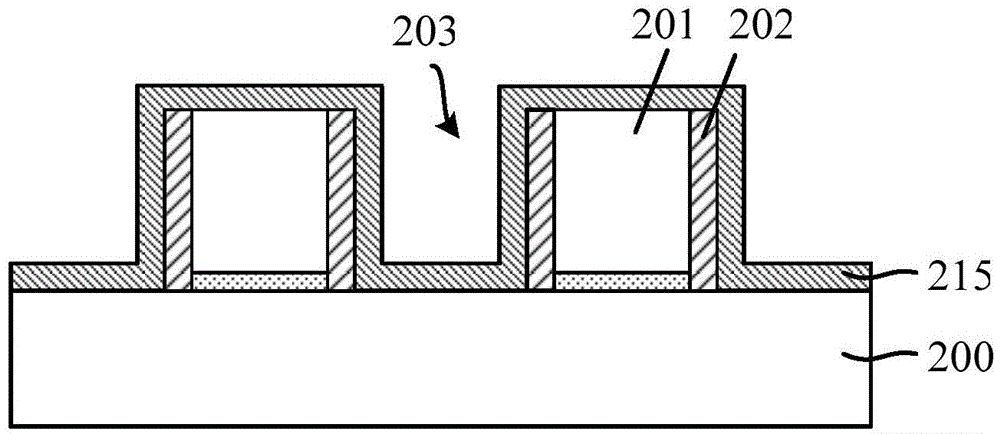

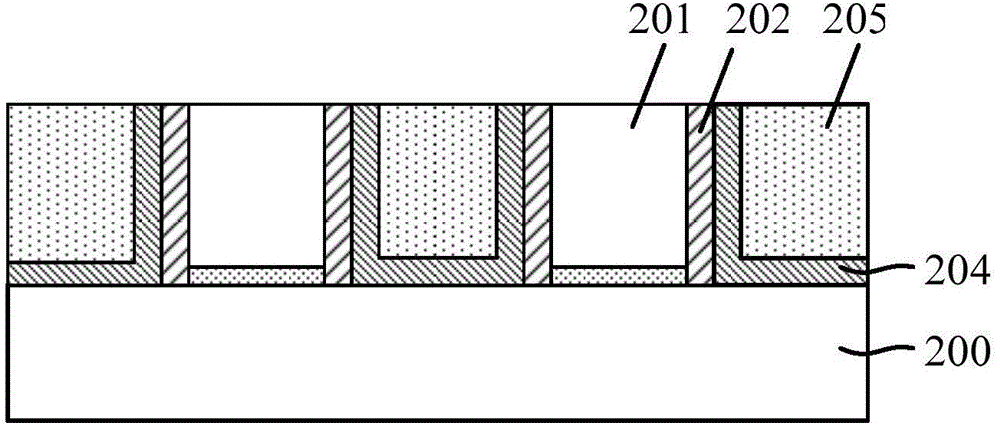

[0031]In the prior art, in the process of forming metal plugs connecting the source / drain regions, after forming the first dielectric layer, it is necessary to form a photoresist layer with openings on the first dielectric layer, and then use the photoresist layer as a mask, etch the first dielectric layer to form etching holes in the first dielectric layer, but as the integration of devices continues to increase, the distance between adjacent gate structures is also getting smaller and smaller, which means It is required that the size of the opening formed in the photoresist layer is also continuously reduced, and is limited by the photolithography equipment and process conditions. When the size of the opening formed in the photoresist layer is very small (less than 80 nanometers), it can be developed by exposure The opening formed in the photoresist layer by the process is prone to shift in position, so that the position of the etching hole formed by etching the first dielect...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com