Analytical method for total dose effect sensitivity of logic gate circuits and cmos digital circuits

A logic gate circuit and total dose effect technology, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve the problems of lack of screening methods, increased layout area, and reduced integration, so as to facilitate automatic operation and simplify analysis Process, the effect of saving layout area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The present invention will be described in detail below.

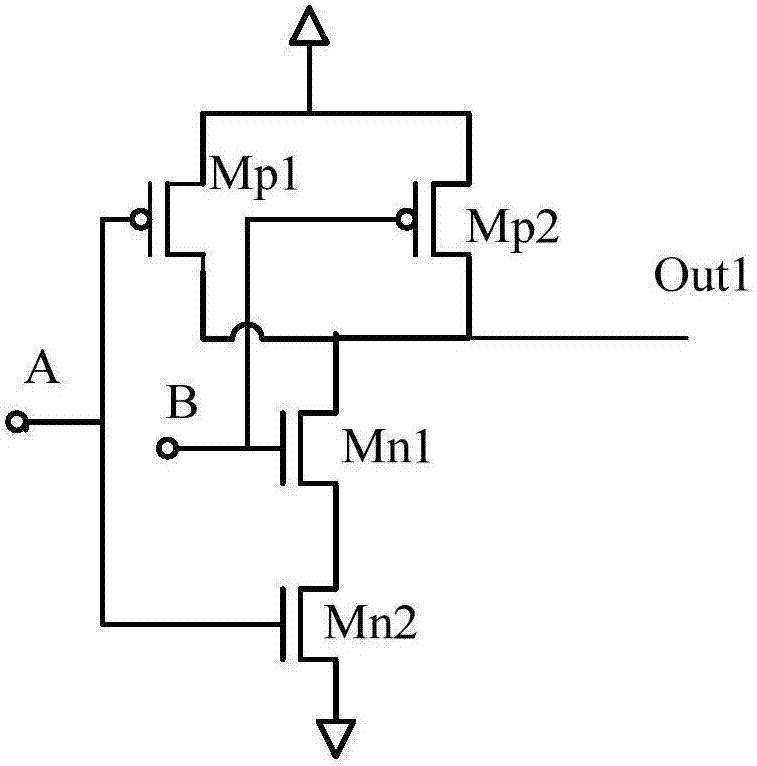

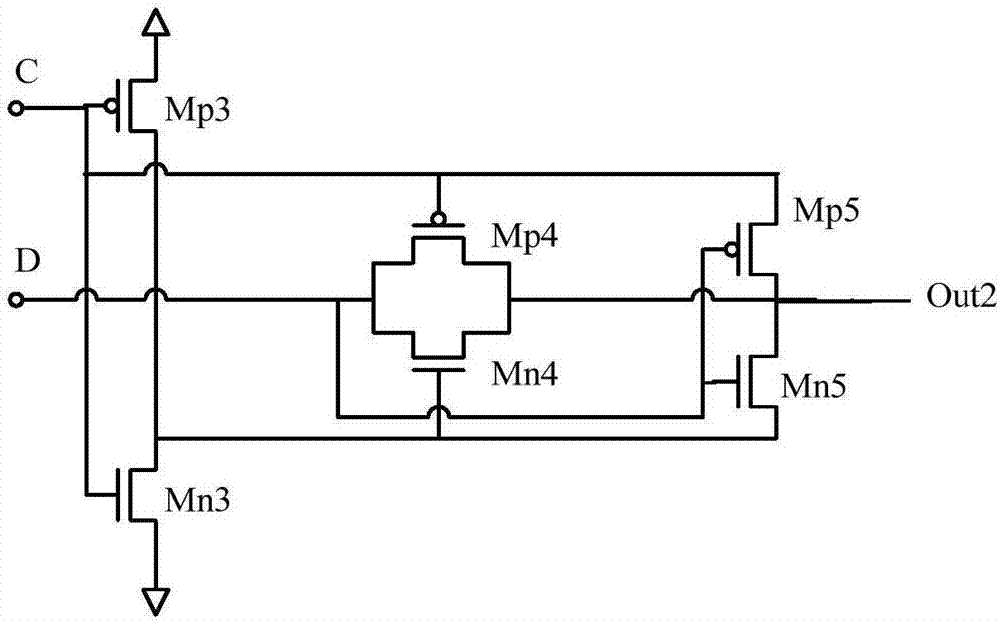

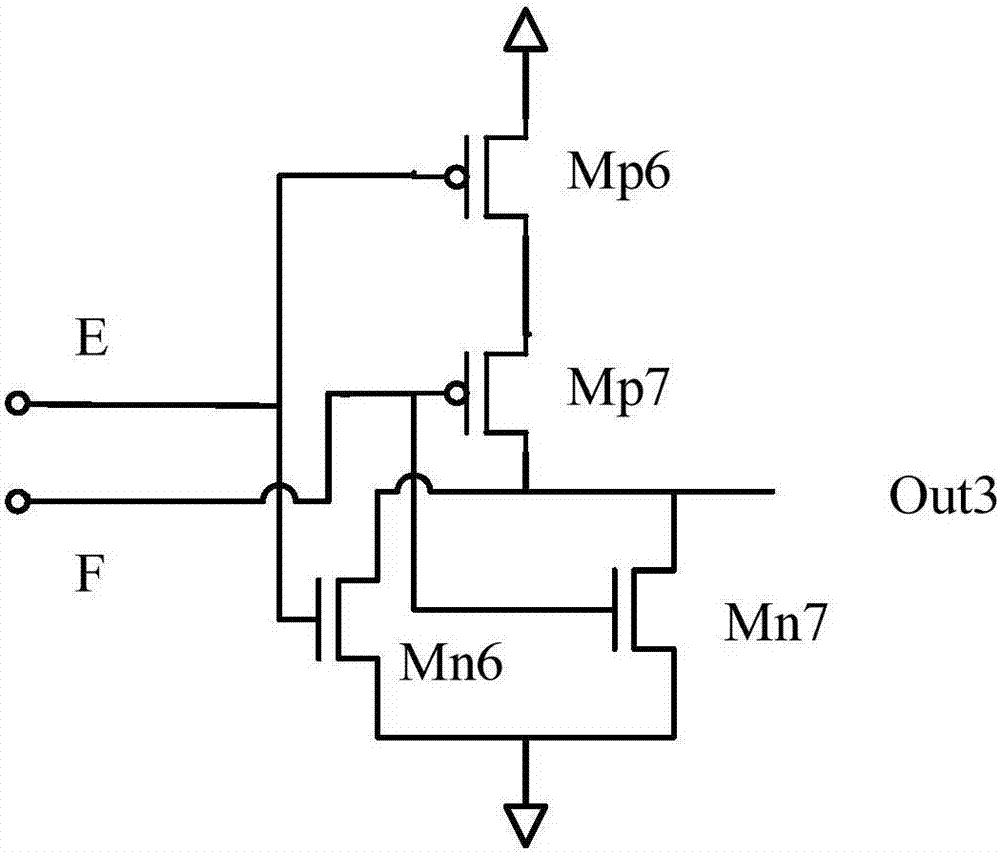

[0030] For the current general-purpose deep submicron or nanometer process integrated circuits, the total dose damage mainly affects the nMOS tubes, especially the nMOS tubes connected to high levels during the irradiation process, and the corresponding electrical characteristics of the pMOS tubes drift Almost negligible. Based on this consideration, when screening the total dose sensitivity of the circuit, it is only necessary to examine the combined state of high-level input signals during the irradiation process, and the combination of low-level input signals during the irradiation process can be directly eliminated .

[0031] The total dose damage of CMOS circuits is mainly characterized by the gradual decrease of the output high level value with the increase of the cumulative dose. When the amplitude of the output high level is low to a certain extent, it may be misidentified as a logic low level by the ba...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com