Manufacturing method of embedded source/drain MOS transistor

A technology of a MOS transistor and a manufacturing method, which is applied in the manufacturing field of embedded source/drain MOS transistors, can solve problems such as reducing the epitaxial growth rate of silicon germanium, and achieve the effect of preventing adhesion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

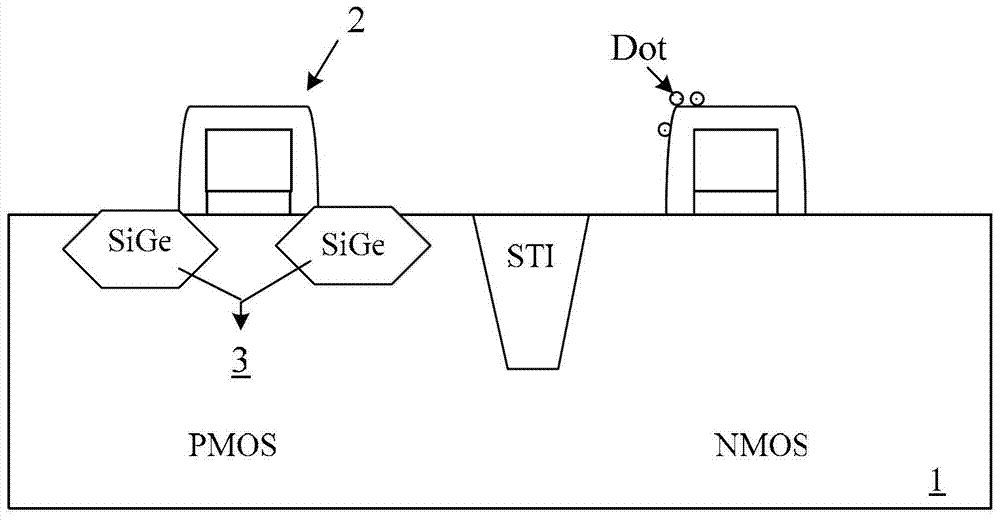

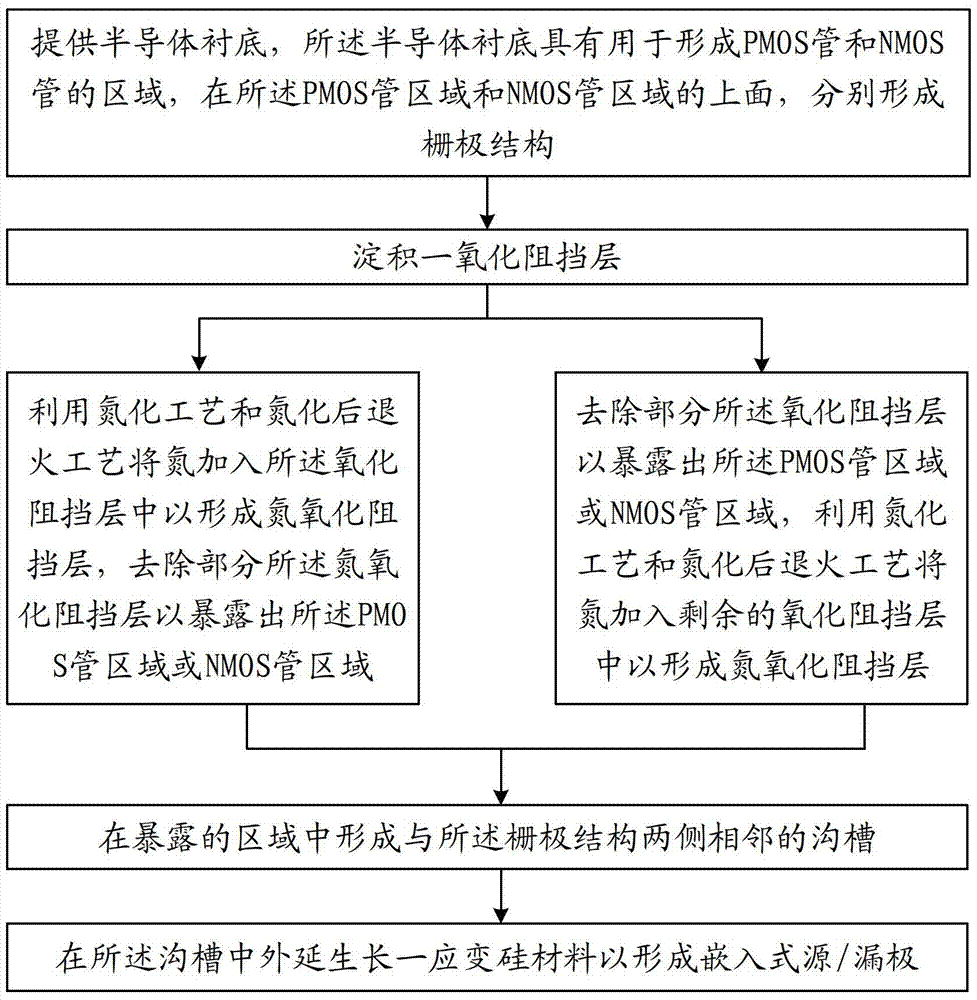

[0030] by figure 2 The manufacturing flow shown is an example, combined with Figure 3a to Figure 3f , a method for manufacturing an embedded source / drain MOS transistor provided by the present invention will be described in detail.

[0031] In step S1, see Figure 3a , provide a semiconductor substrate 10, the semiconductor substrate 10 has at least a region for forming a PMOS transistor and an NMOS transistor region, a gate structure 12 is formed on the PMOS transistor region, and also in the NMOS transistor region The same gate structure 12 is also formed above. The gate structure 12 includes a gate oxide layer 12-1, a polysilicon gate 12-2 located on the semiconductor substrate from bottom to top, and a gate side surrounding the gate oxide layer 12-1 and the polysilicon gate 12-2. Wall 12-3.

[0032] Further, a shallow trench isolation (STI) for insulating the PMOS transistor region and the NMOS transistor region is also formed on the semiconductor substrate 10 .

[0...

Embodiment 2

[0040] by figure 2 The manufacturing flow shown is an example, combined with Figure 3a-3b and 3g to Figure 3j , a method for manufacturing an embedded source / drain MOS transistor provided by the present invention will be described in detail.

[0041] The contents in steps S1 and S2 in this embodiment are the same as those in steps S1 and S2 in the first embodiment, and will not be repeated here. For specific contents and corresponding parameters, please refer to step S1 in the first embodiment , S2.

[0042] In step S3, see Figure 3g , taking the NMOS tube area as an example, the oxidation barrier layer 14 covering the NMOS tube area to be exposed is removed to expose the NMOS tube area, while the unremoved oxidation barrier layer 14 still covers the PMOS tube area.

[0043] Then, see Figure 3h , using DPN technology to add nitrogen into the remaining oxidation blocking layer 14 , and then using PNA technology to stabilize the nitrogen added to the oxidation blocking ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com