Graph pattern decomposition method adopting triple patterning photoetching technology

A technology of triple exposure and photolithography technology, which is applied in special data processing applications, instruments, electrical digital data processing, etc., and can solve problems such as the decline in chip yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

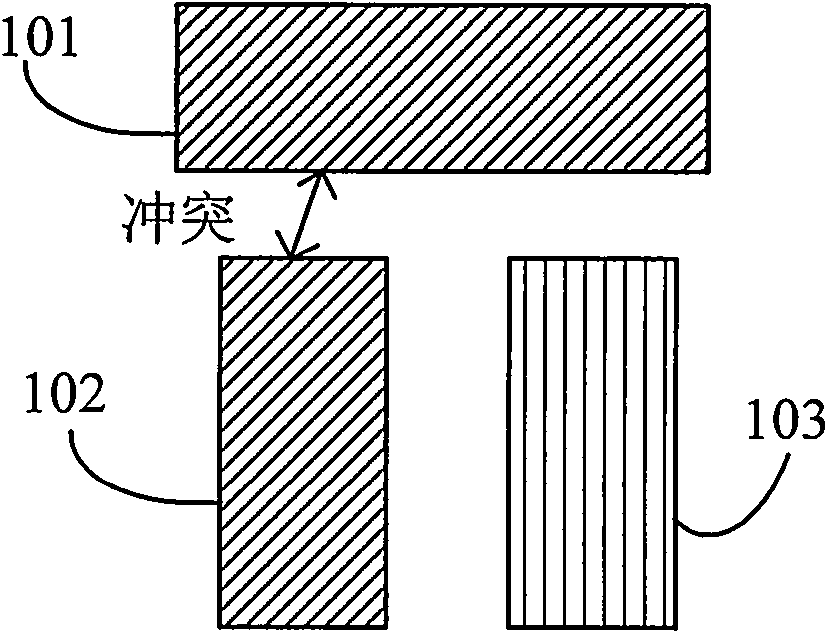

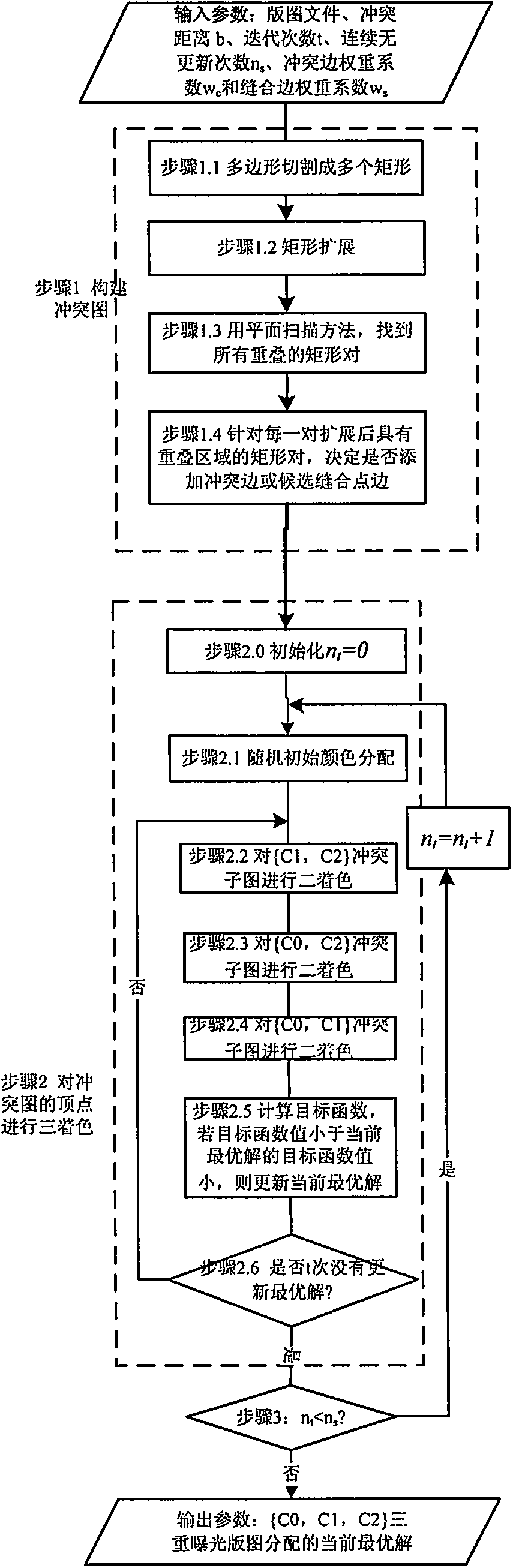

[0072] The pattern in the input layout file is as Figure 7 As shown, it needs to be triple-exposure layout pattern assignment. Among them, 1, 2, 3, and 4 are polygon layout patterns. Set the number of iterations n s = 30, the number of consecutive no updates t = 3, the conflict edge weight coefficient w c =10, seamed edge weight coefficient w s =1.

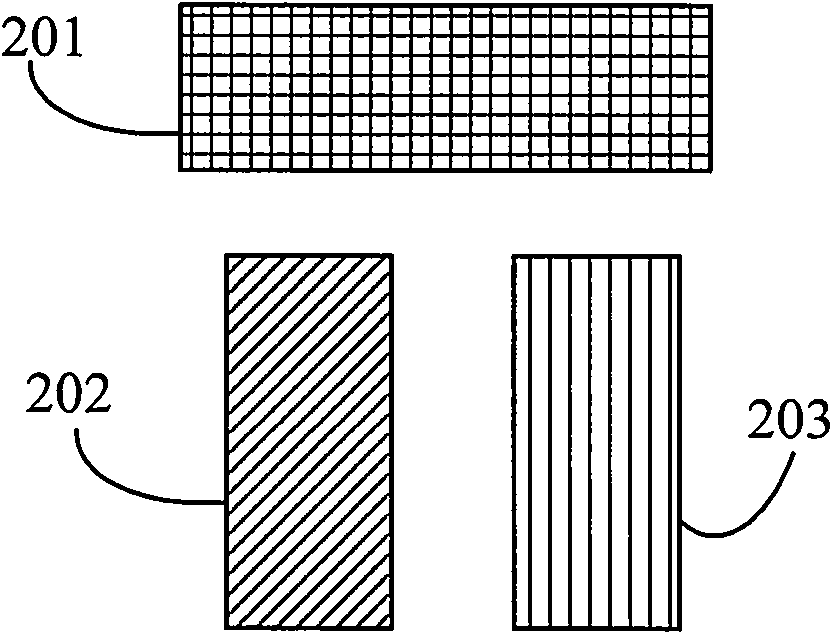

[0073] As described in step 1.1, the Figure 7 The polygon in is cut into several rectangles, such as Figure 8 shown. Among them, polygon 2 is cut into rectangle 21 and rectangle 22 , and polygon 4 is cut into rectangle 41 and rectangle 42 . According to step 1.2, expand the sides of each rectangle outward by b / 2, and then construct the conflict graph according to the methods described in steps 1.3 to 1.4. The result is as follows Figure 8 As shown in , where the rectangles are expressed as vertices in the conflict graph, the solid lines indicate that there are conflicting edges between the rectangles, and the edge weig...

Embodiment 2

[0085] The method of the present invention is realized with C++ programming language, and runs on a 64-bit 2.66GHz CPU and a linux machine with 4GB memory. The test layout comes from the layout of the first metal layer in the ISCAS-85&89 test case. Set conflict distance b=160nm, conflict edge weight coefficient W c =10, seamed edge weight coefficient W s = 1, the number of iterations n s =30, continuous no update times t=3; Experimental results are as shown in table 1, wherein #C, #S, COST, imp represent respectively the number of conflicts after decomposing the layout with the method of the present invention, stitching point number, objective function and the present invention The COST improvement ratio compared to the corresponding method. Compared with two methods in prior art document [8] and document [9], the improvement effect of the present invention's method can reach 29% and 42.2% the highest respectively (improvement effect is defined as: (COST of other methods-th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com