3D assembling method for integrally integrating chips of T/R assembly

An assembly method and chip technology, applied in the fields of semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problem of unsuitable T/R component design and assembly, no telecommunication signal chip design combination, no transmitting function and receiving function. function and other issues, to achieve the effect of fast signal transmission, reduced volume and weight, and reduced size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

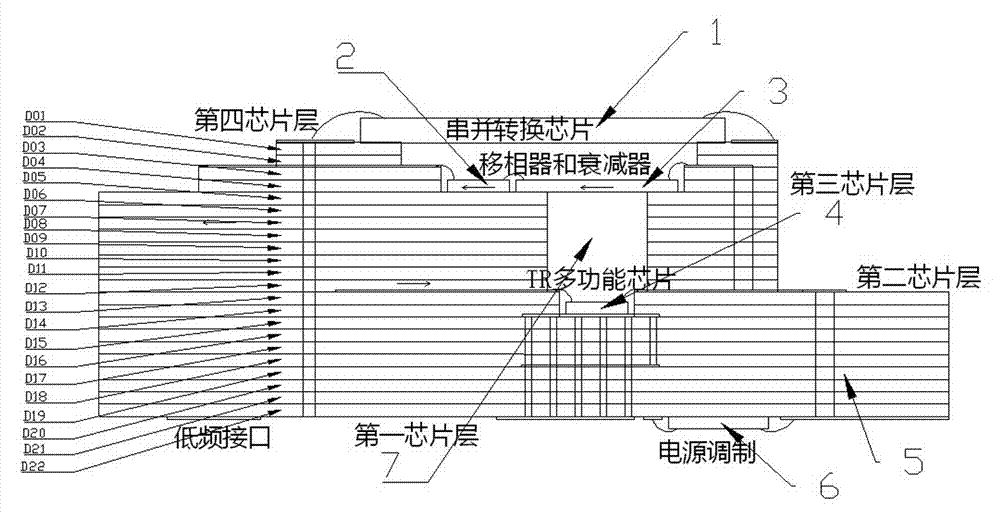

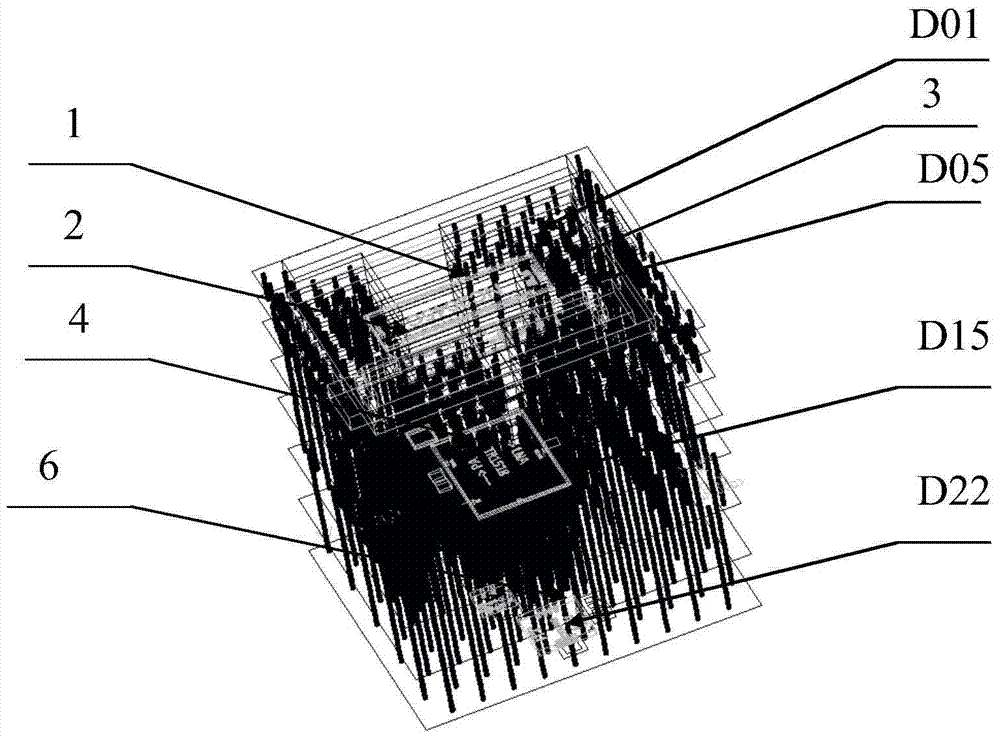

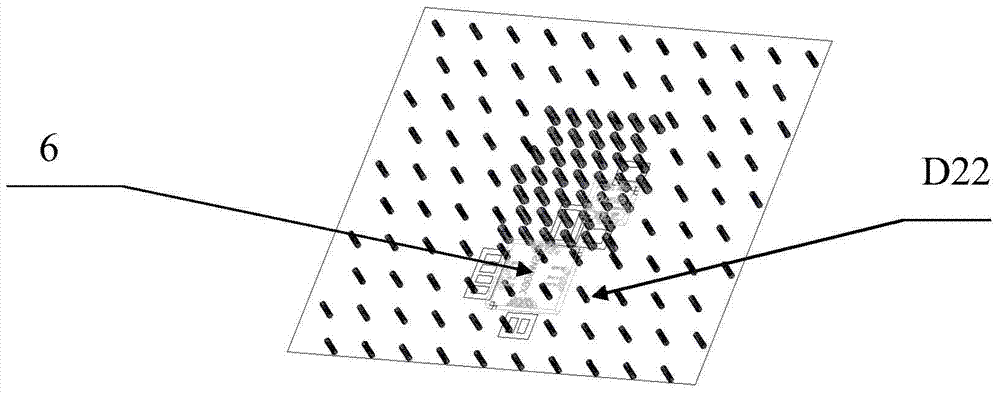

[0026] refer to Figure 1 to Figure 5 . In a best implementation case described below, the T / R component of the millimeter-wave active phased array antenna working in the Ku (14-18GHz) band, the 3D assembly structure of the T / R component chip mainly includes the LTCC substrate, through The serial-to-parallel conversion chip 1, the phase shifter (2), the attenuator 3, the T / R multi-function chip 4 and the power modulator 6 connected together by the transmission line and the vertical interconnection. The large-area metal ground and metal transmission line used for chip bonding in the LTCC substrate used as the chip carrier layer and chip interconnection are all gold layers. The top and bottom surfaces of the LTCC substrate are solderable grounding areas, which are interconnected with the internal grounding metal layer of the LTCC substrate through metallized through holes. The conductive adhesive is used to realize the bonding assembly of the T / R component chip and the LTCC su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com