Bias voltage temperature instability testing circuit and testing method thereof

A technology for testing circuits and instability, applied in the field of integrated circuit reliability testing, can solve the problem of inability to distinguish the degree of the influence of the PMOS tube negative bias temperature unstable oscillation frequency, etc., to improve reliability and increase sensitivity. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

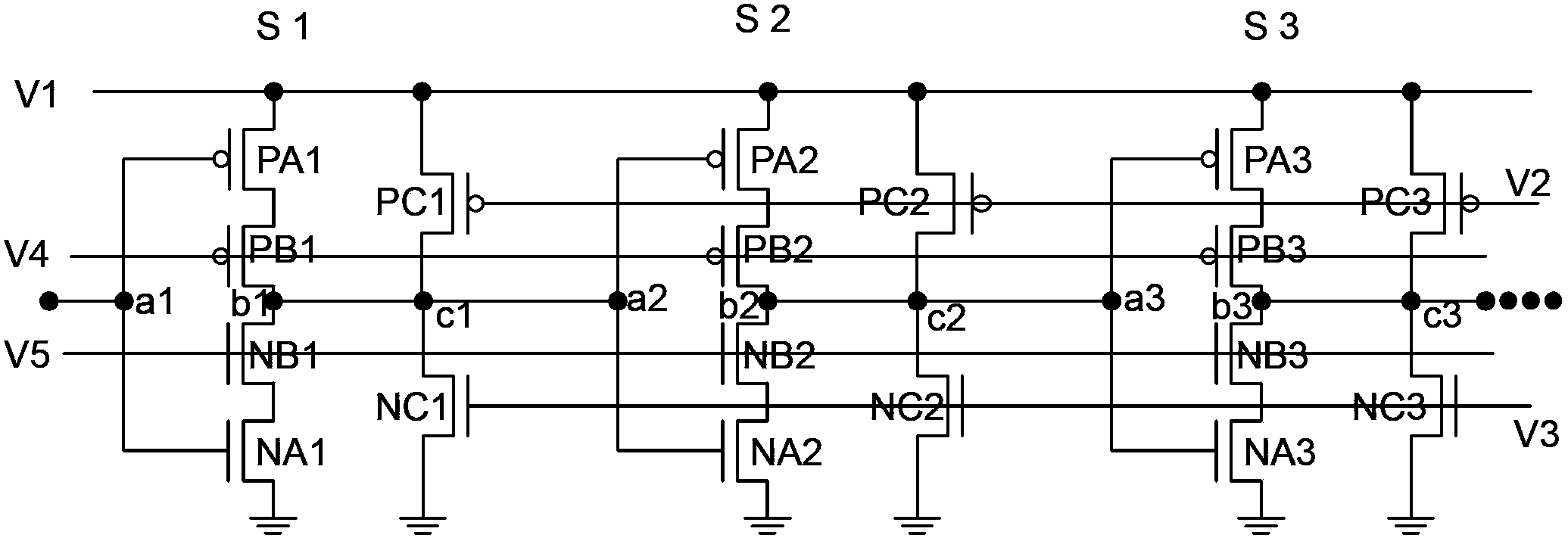

[0061] Please refer to the following figure 2 , which is a schematic diagram of the bias temperature instability test circuit according to the first embodiment of the invention.

[0062] The bias temperature instability test circuit of the present invention includes a ring resonator circuit and n-level test circuits, and each level of test circuits includes a pair of complementary PMOS transistors to be tested and NMOS transistors to be tested, a pair of complementary switch PMOS transistors and A switch NMOS transistor and a pair of complementary voltage-dividing PMOS transistors and voltage-dividing NMOS transistors.

[0063] like figure 2 As shown, in this embodiment, the bias temperature instability test circuit is based on a ring resonator circuit, and the ring oscillator circuit includes n-level test circuits, each of which has the same structure, where n is positive integer, in figure 2 Among them, S1 is the first-level test circuit, S2 is the second-level test ci...

no. 2 example

[0076] Please refer to the following Figure 5, which is a schematic diagram of a bias temperature instability test circuit according to the second embodiment of the invention. The second embodiment is based on the first embodiment, the difference is that the bias temperature instability testing circuit of the second embodiment further includes a transmission gate. A transmission gate is connected between the third node of each test circuit and the first node of the next test circuit. When k is 2, such as Figure 5 As shown, the second-level test circuit further includes a transmission gate, one end of the transmission gate is connected to the third node c2 in the second-level test circuit, and the other end of the transmission gate is connected to the first node a3 in the third-level test circuit . One end of the transmission gate in the n-level test circuit is connected to the third node cn in the n-level test circuit, and the other end is connected to the first node a1 i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com