Tunneling field effect transistor of vertical structure and preparation method thereof

A technology of tunneling field effect and vertical structure, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of large leakage current and small drive current of planar tunneling field effect transistors, and achieve improved drive current, suppress leakage current, and increase the effect of tunneling area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

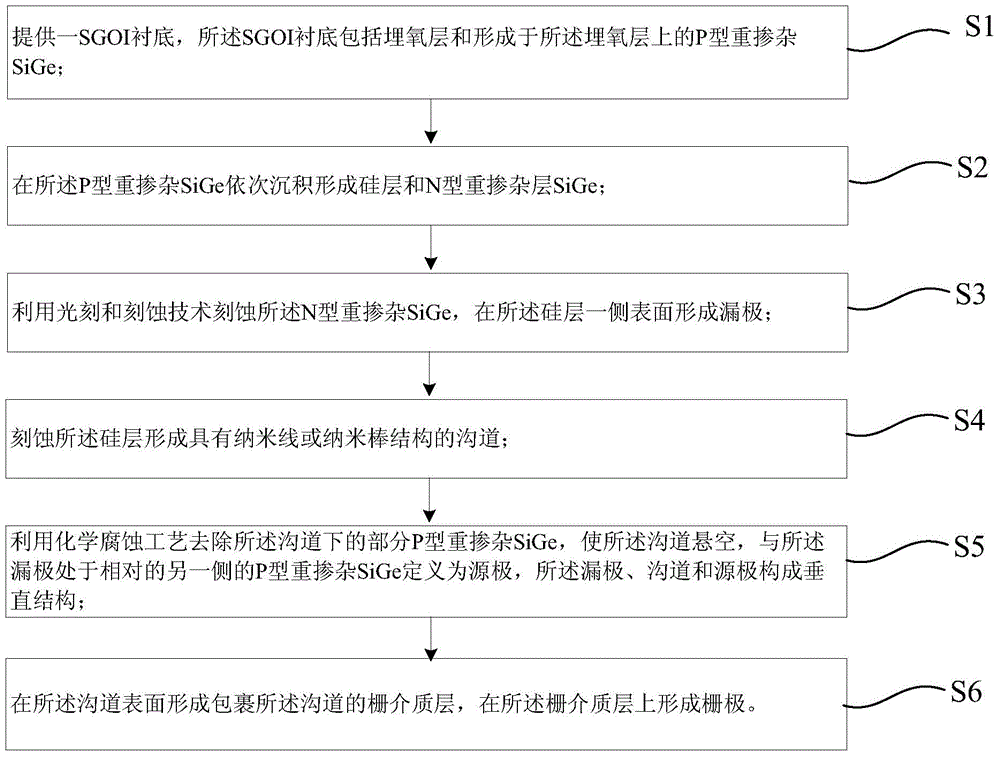

[0046] The invention provides a method for preparing a tunneling field effect transistor with a vertical structure, such as figure 1 As shown in the process flow chart, the preparation method of the tunneling field effect transistor with vertical structure at least includes the following steps:

[0047] S1, providing an SGOI substrate, the SGOI substrate including a buried oxide layer and P-type heavily doped SiGe formed on the buried oxide layer;

[0048] S2, sequentially depositing a silicon layer and N-type heavily doped SiGe on the P-type heavily doped SiGe;

[0049] S3, using photolithography and etching techniques to etch the N-type heavily doped SiGe to form a drain on one side of the silicon layer;

[0050] S4, etching the silicon layer to form a channel with a nanowire or nanorod structure;

[0051]S5, using a chemical etching process to remove part of the P-type heavily doped SiGe under the channel, so that the channel is suspended, and the P-type heavily doped SiG...

Embodiment 2

[0076] The present invention also provides a tunneling field effect transistor with a vertical structure, which is made by using the preparation method provided in Embodiment 1. The tunneling field effect transistor with a vertical structure at least includes:

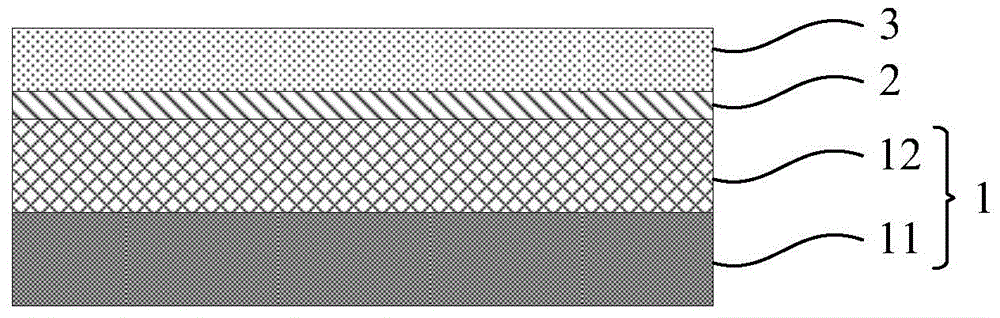

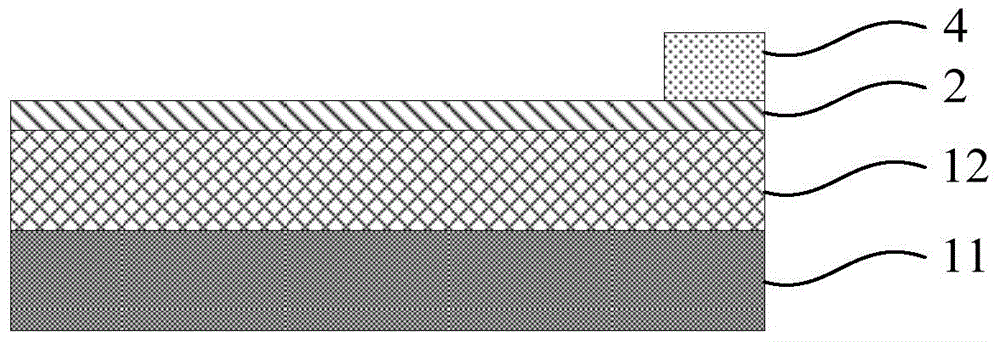

[0077] The SGOI substrate 1 includes a buried oxide layer 11 and P-type heavily doped SiGe12 located on both sides of the buried oxide layer 11, wherein the P-type heavily doped SiGe12 on one side is defined as a source 121;

[0078] A channel 21 with a nanowire or nanorod structure suspended over the P-type heavily doped SiGe12;

[0079] The drain 4 is combined with the P-type heavily doped SiGe12 on the other side opposite to the source 121, and the source 121, the channel 21 and the drain 4 form a vertical structure;

[0080] a gate dielectric layer 5 wrapped on the surface of the channel 21;

[0081] The gate 6 is formed on the gate dielectric layer 5 .

[0082] The width of the channel 21 of the nanowire or nano...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com