Tunnel Field Effect Transistor and Manufacturing Method

A technique of tunneling field effect and manufacturing method, which is applied in the field of tunneling field effect transistors and its manufacturing, can solve problems such as inability to manufacture logic circuits, difficulty in wide-scale application, and increased resistance value, and achieve large tunneling area and strong Spin-orbit coupling, performance-enhancing effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] In order to further improve the performance of the existing tunneling field-effect transistor (The tunneling field-effect transistor, TFET), the present invention provides a manufacturing method of the tunneling field-effect transistor, comprising:

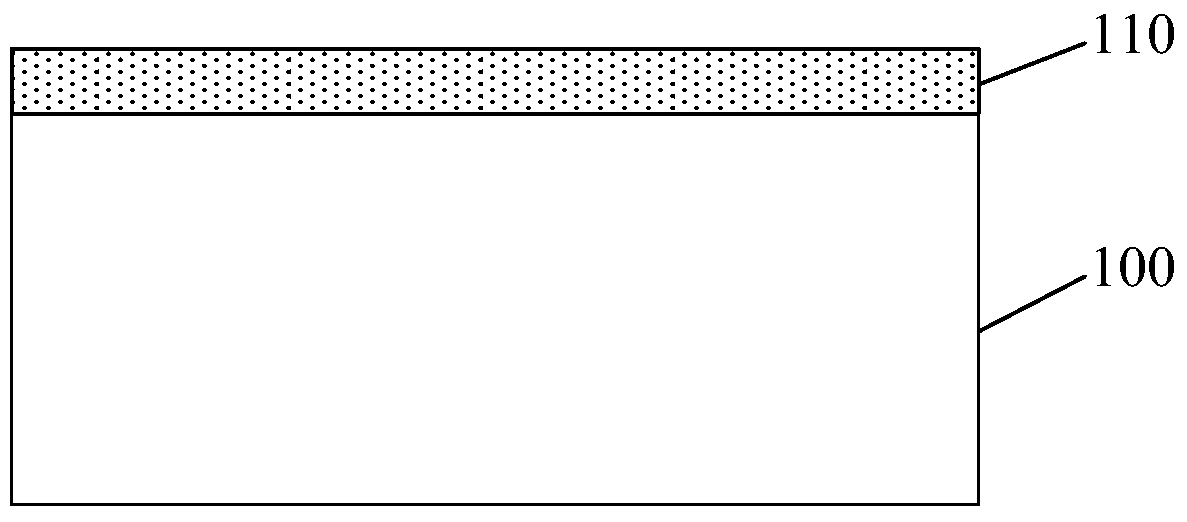

[0046] provide the substrate;

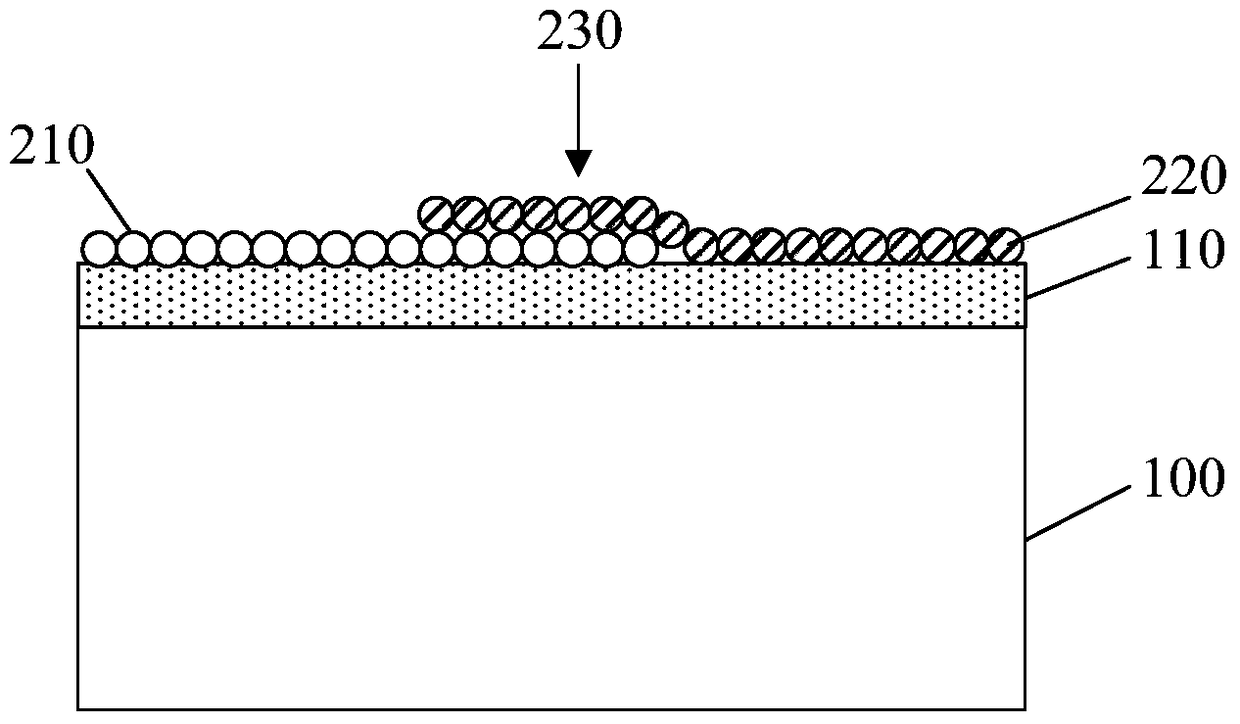

[0047] forming a P-type silicene layer and an N-type silicene layer on the substrate, so that the P-type silicene layer and the N-type silicene layer overlap and contact each other at the junction of the two to form a laminated structure;

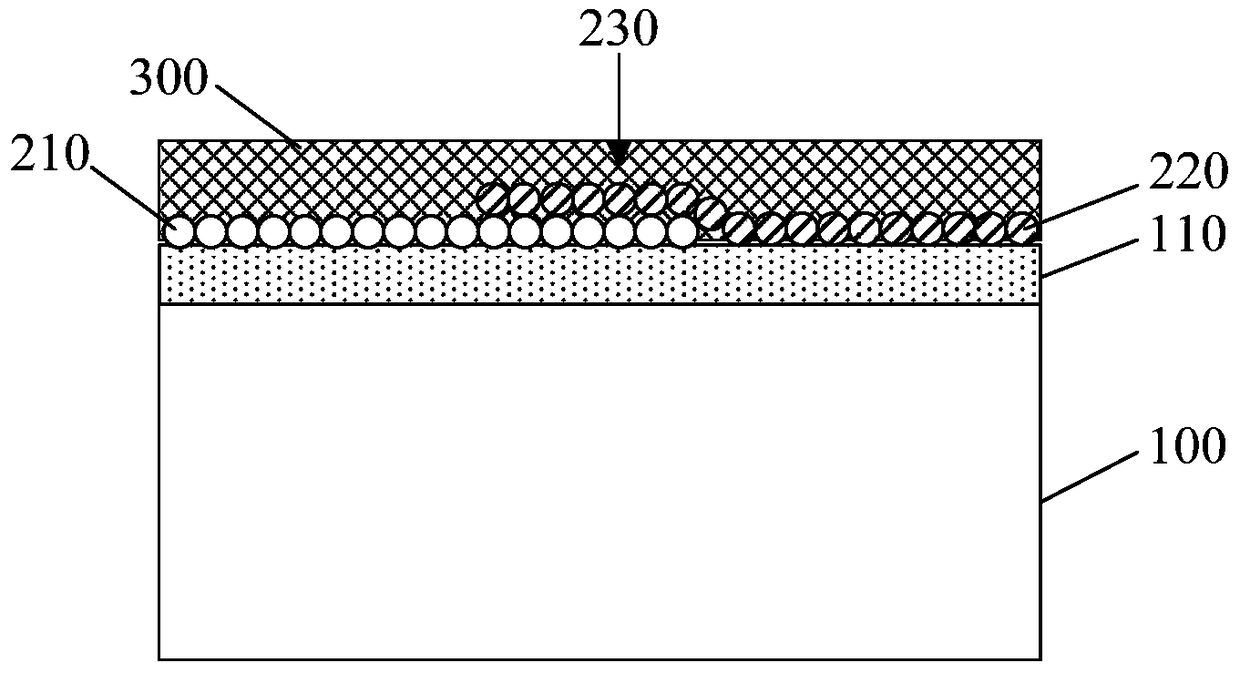

[0048] forming a gate structure on the stacked structure;

[0049] Electrodes are respectively formed on the P-type silicene layer and the N-type silicene layer on both sides of the gate structure to form a source or drain with the P-type silicene layer and the N-type silicene layer.

[0050] Through the above steps to form a tunnel field effect transistor, in which silicene has higher electron mobility and stronger spin-orbit coupling, so it can open a l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com