Tunneling Field Effect Transistor and Method of Forming the Same

A tunneling field effect, transistor technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of sub-threshold swing reduction, low drive current, small on-state current, etc., to increase tunneling Area, increased tunneling path, effect of increased length

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

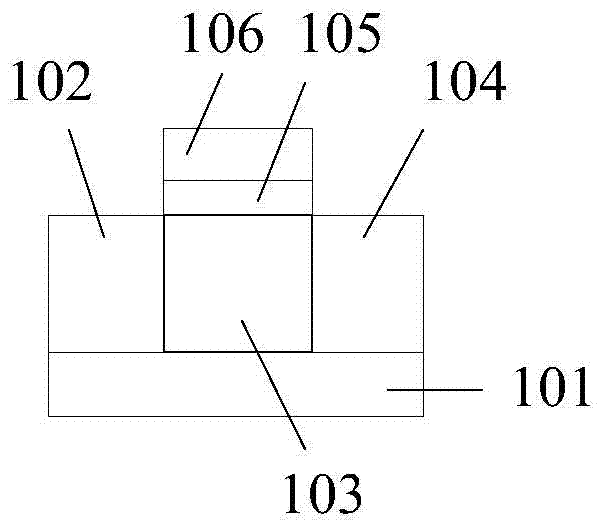

[0055] Existing tunneling field effect transistors cannot achieve high on-state current and low sub-threshold slope, and the tunneling path and tunneling area are the most important factors that determine the performance of tunneling field effect transistors. The long tunneling path and larger tunneling area help to improve the performance of tunneling field effect transistors.

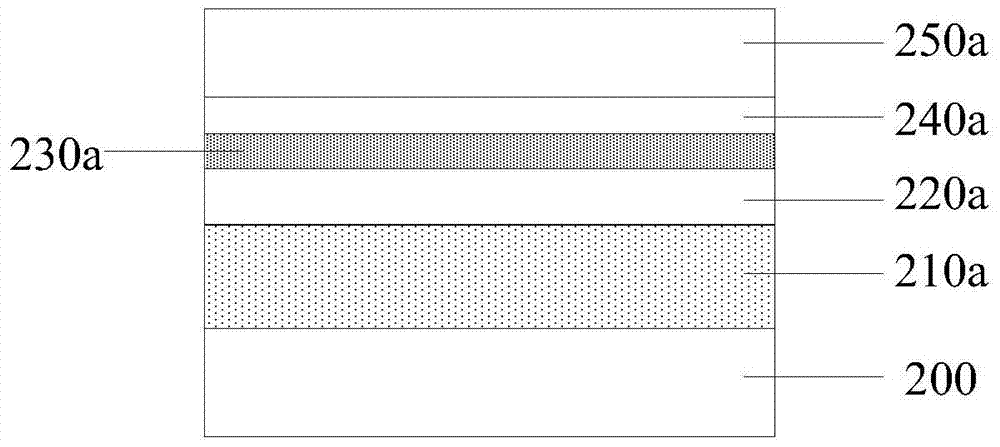

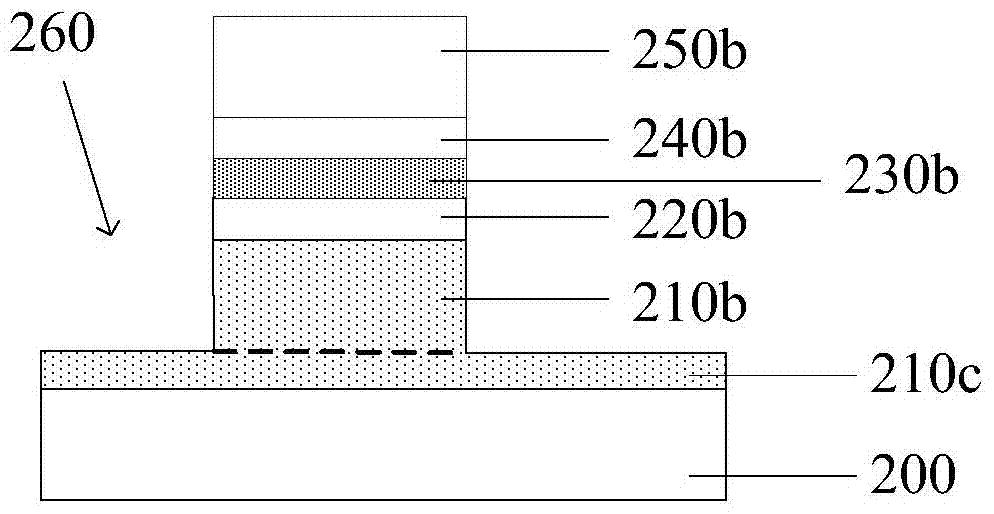

[0056] To this end, the present invention provides a new tunneling field effect transistor having a second channel region surrounding the first doped region, the first channel region and the second doped region at the same time. Since the length of the second channel region is significantly increased, the tunneling path of the transistor is increased, and because the second channel region completely covers the first doped region and the side surfaces of the first channel region, and at least covers the second doped region Therefore, the area of the second channel region is larger, which increases the t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com