Heterojunction, ferroelectric tunnel junction and preparation method and application thereof

A ferroelectric tunnel and heterojunction technology, applied in the field of microelectronic materials, can solve the problems such as the difficulty of direct contact between ferroelectric thin film and semiconductor silicon, and achieve the effects of overcoming the limitation of short shielding length modulation, enhanced tunnel resistance, and good modulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

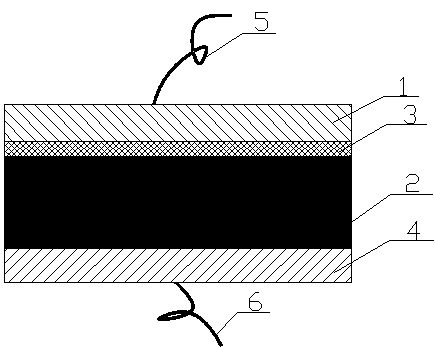

Image

Examples

Embodiment 1

[0051] A method for preparing a ferroelectric / extrinsic silicon semiconductor heterostructure, the preparation steps of which are as follows:

[0052] a) The doped P-type or N-type (001) oriented single crystal silicon semiconductor substrate is cleaned for half an hour by using an ultraviolet ozone cleaner, and then loaded into a molecular beam epitaxy (MBE) chamber.

[0053] b) Use a vacuum pump to pump the vacuum in the growth chamber to 3.0×10 -7 Below Pa.

[0054] c), specifically heating the substrate to 600-700°C and depositing ~ 8 ? thick strontium.

[0055] d), heating the substrate to 750 oC -850oC, SiO 2 The layer desorbs and falls off, and the surface treatment ends when no shedding falls off.

[0056] e), again pumping the vacuum in the growth chamber to 3.0×10 -7 Below Pa.

[0057] f), control the substrate temperature at 300 oC ~350 o Between C.

[0058] g) Precisely control the flux of strontium and titanium flow at 10 16 atoms / m 2 ·s-10 18 atoms / ...

Embodiment 2

[0065] The preparation method of the resistive switching device unit based on metal / ferroelectric / extrinsic silicon semiconductor heterogeneous FTJ, the specific preparation steps are as follows:

[0066]a) Surface treatment and deposition of strontium titanate ferroelectric thin film on doped P-type or N-type (001) oriented single crystal silicon semiconductor substrate according to the method of Example 1.

[0067] b) Removal of SrTiO from the MBE growth chamber 3 / (001) Si heterojunction, cover with a mask, and use magnetron sputtering or other coating methods to grow Pt or Au electrodes with a thickness of 100 nm-150 nm;

[0068] c) Print a layer of back electrode on the back of the semiconductor extrinsic silicon substrate: the circular aluminum paste is printed on the whole area, and a 2mm gap is reserved around it, and then the 800 o C-900 o C sintering 50s-60s;

[0069] d) Finally, the lead wires of copper grade and gold are respectively connected from the upper and...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com