Correction method and corrector for time-interleaved adc sampling time mismatch

A technology of sampling time and time interleaving, applied in the field of microelectronics, can solve problems affecting the dynamic performance of analog-to-digital converters, and achieve the effects of guaranteed performance, improved performance, and low complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

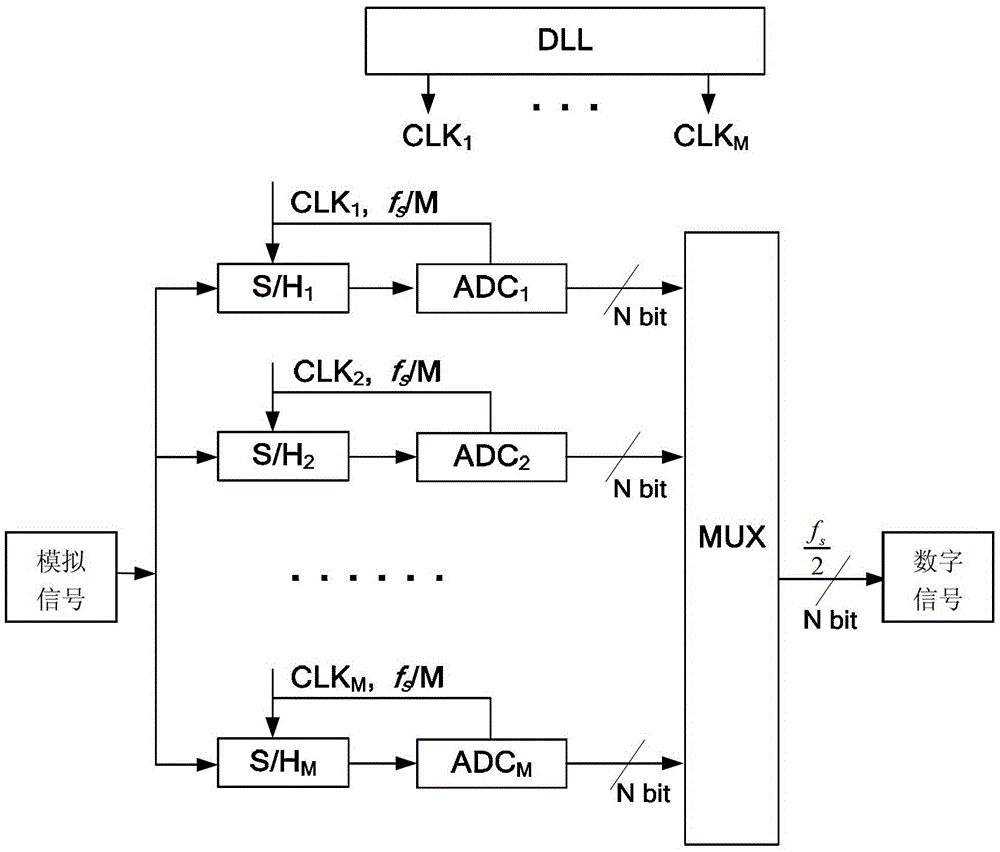

[0050] Taking the four-channel time-interleaved ADC as an example, such as Figure 4 As shown, its working principle is: the four clocks generated by the DLL are respectively sent to the sample and hold modules of the four channels, and the working time of the sample and hold modules of each channel is staggered. The channel ADC converts the output of the sample and hold module into a frequency fs / 8, N-bit digital codeword (wherein, f s interleaves the sampling frequency of the ADC for the entire time). The output of the channel ADC is sent to the multiplexer, and the multiplexer converts the output of each channel ADC into a frequency f s / 2 N-bit digital output.

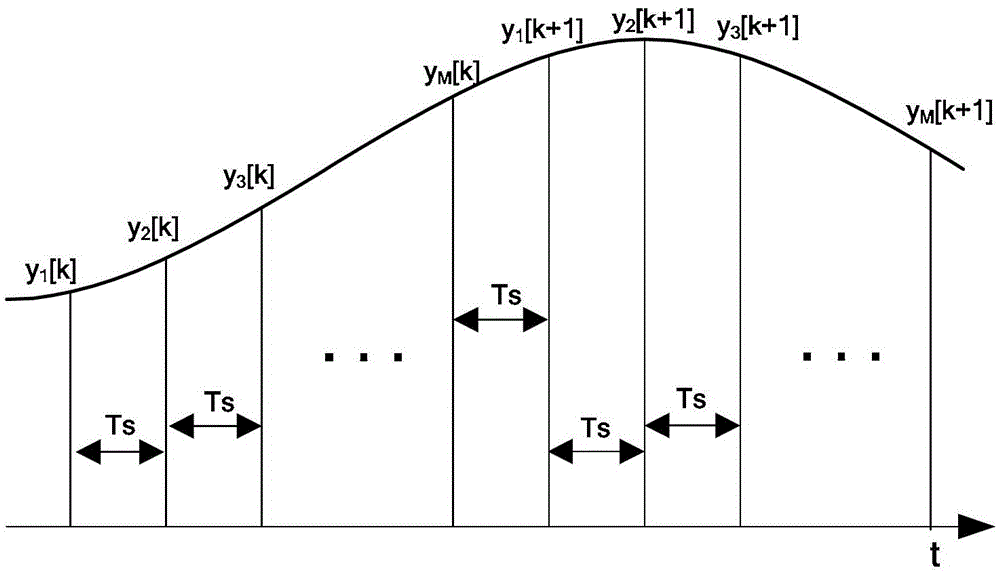

[0051] When there is no sample time mismatch between channels, such as Figure 5 Shown by the solid line in the middle vertical line.

[0052] make:

[0053] E 1 [ k ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com