Sampling clock?mismatch?background?correction method based on time-to-digital?converter

A sampling clock and time digital technology, applied in the direction of analog/digital conversion calibration/testing, etc., can solve problems affecting the dynamic performance of analog-to-digital converters, and achieve the effects of guaranteed performance, low complexity, and improved performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

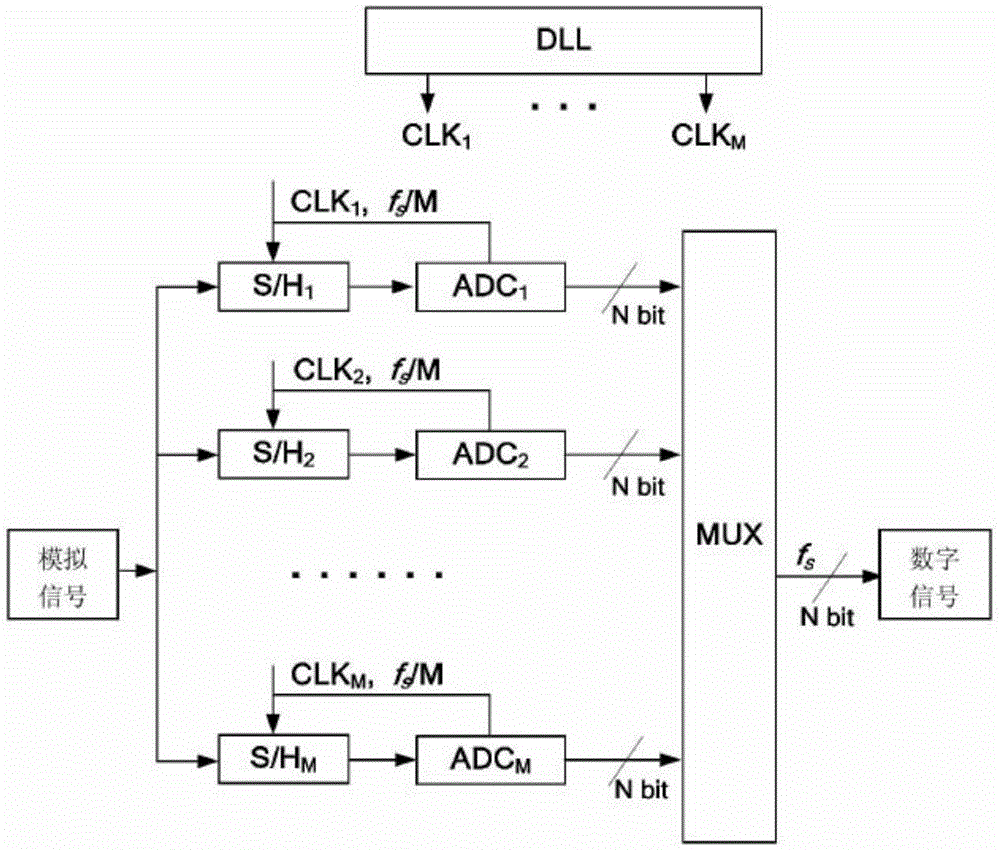

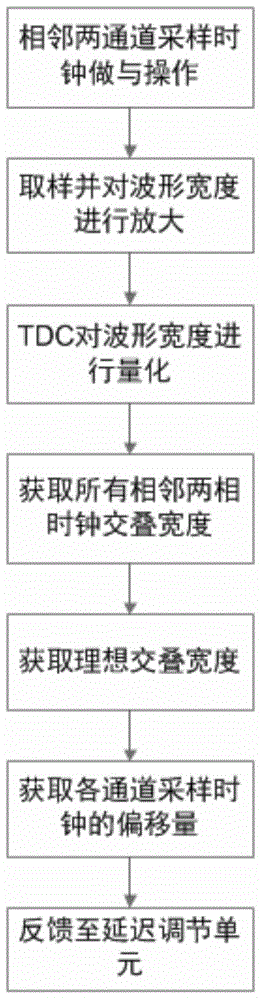

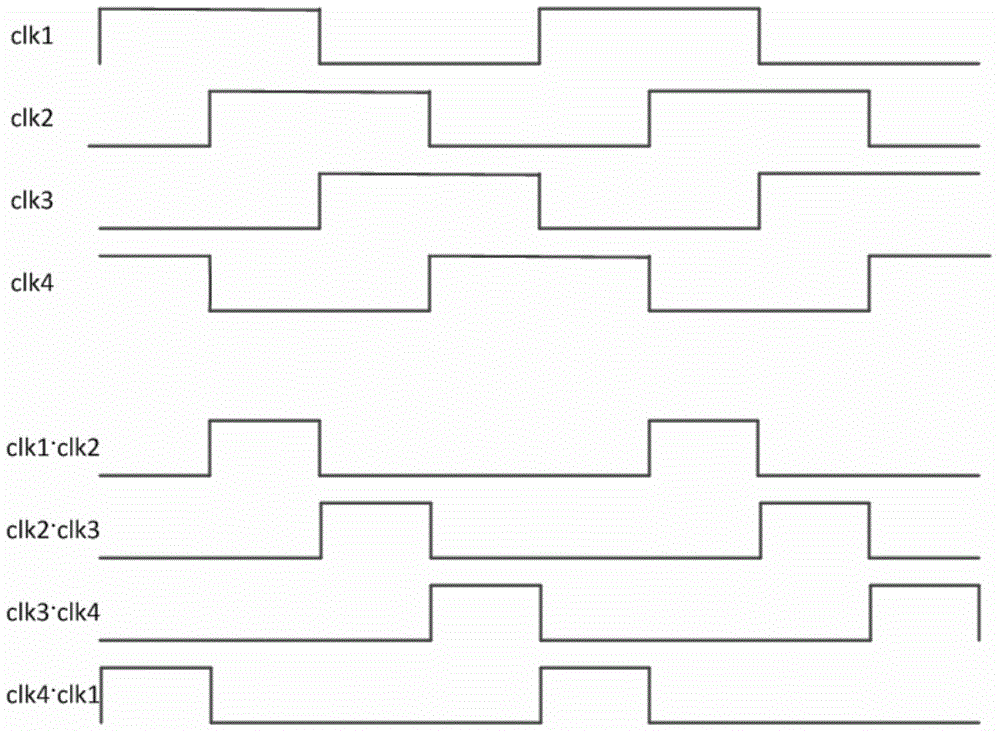

[0029] The invention aims to propose a background correction method for sampling clock mismatch based on a time-to-digital converter, which performs background correction on the sampling clock mismatch of a time-interleaved analog-to-digital converter, and improves the performance of the time-interleaved analog-to-digital converter. The solution of the present invention can be summarized as: doing an AND operation on adjacent sampling clocks of each two phases of a time-interleaved analog-to-digital converter (hereinafter referred to as time-interleaved ADC), and obtaining the overlapping waveform A of adjacent sampling clocks i , using a time domain waveform width amplifier pair A i The width of C is enlarged to obtain C i , using a time-to-digital converter (hereinafter referred to as TDC) for C i Quantify to get D i ,D i The mean value D of represents the digital code corresponding to the ideal overlapping width of adjacent two-phase clocks, by calculating E i =D i -D ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com