A Received Signal Strength Indicating Circuit with Reduced Layout Area

A technology that reduces the strength of the received signal and the area. It is used in receiver monitoring, electrical components, transmission monitoring, etc., and can solve the problems of poor passband flatness, difficult to determine, and high lower cutoff frequency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

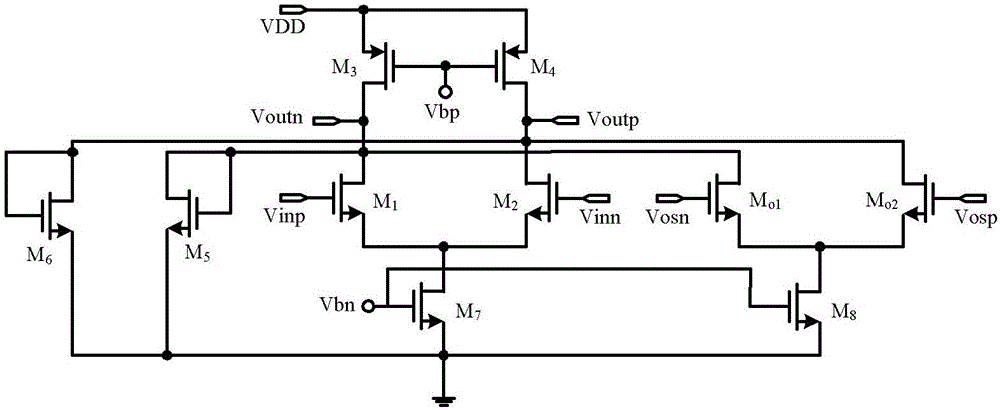

[0060] Such as figure 1 as shown, figure 1 It is a block diagram of an RSSI circuit with a reduced layout area according to an embodiment of the present invention, and the circuit includes a subtractor, a limiting amplifier chain, a full-wave rectifier group, an output buffer, and a DC offset extraction circuit. Among them: the subtractor is used to subtract the intermediate frequency signal input from the outside and the DC offset voltage input from the DC offset extraction circuit, and output the obtained signals to the limiting amplifier chain and the first-stage full-wave rectifier respectively; The amplitude amplifier chain includes a plurality of limiting amplifiers connected in series. The intermediate frequency s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com