Gate-grounded NMOS manufacturing method

A manufacturing method, semiconductor technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

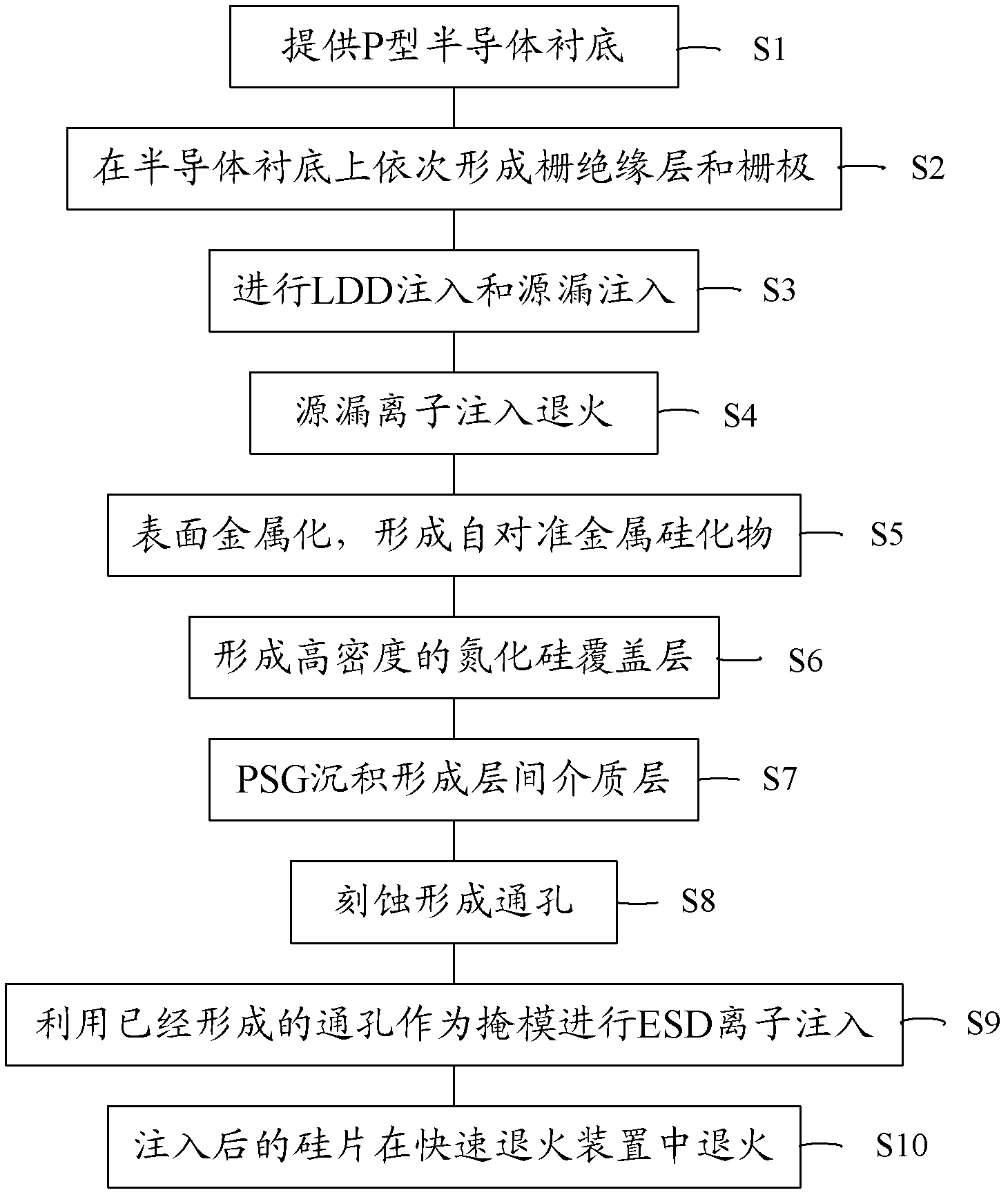

[0026] The present invention uses ESD Implant in the contact hole after the contact hole is formed on the source and drain and before filling the metal plug, which reduces the steps of the original process, reduces the area of the ESD Implant in the drain, and improves the static electricity of the GGNMOS. protective properties.

[0027] The concrete steps that the present invention makes GGNMOS include:

[0028] Step S1: providing a P-type semiconductor substrate;

[0029] Step S2: sequentially forming a gate insulating layer and a gate on the semiconductor substrate;

[0030] Step S3: performing LDD injection and source-drain injection;

[0031] Step S4: source-drain ion implantation annealing;

[0032] Step S5: Surface metallization to form salicide;

[0033] Step S6: forming a high-density silicon nitride capping layer;

[0034] Step S7: PSG is deposited to form an interlayer dielectric layer;

[0035] Step S8: etching to form a through hole;

[0036] Step S9: per...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com