Six-transistor static random access memory unit and manufacturing method thereof

A memory unit, static random technology, applied in static memory, semiconductor/solid-state device manufacturing, transistors, etc., can solve the problems of shortened device life, low degree of asymmetry, unstable reading and writing, etc., to achieve simple process and reduce cost Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

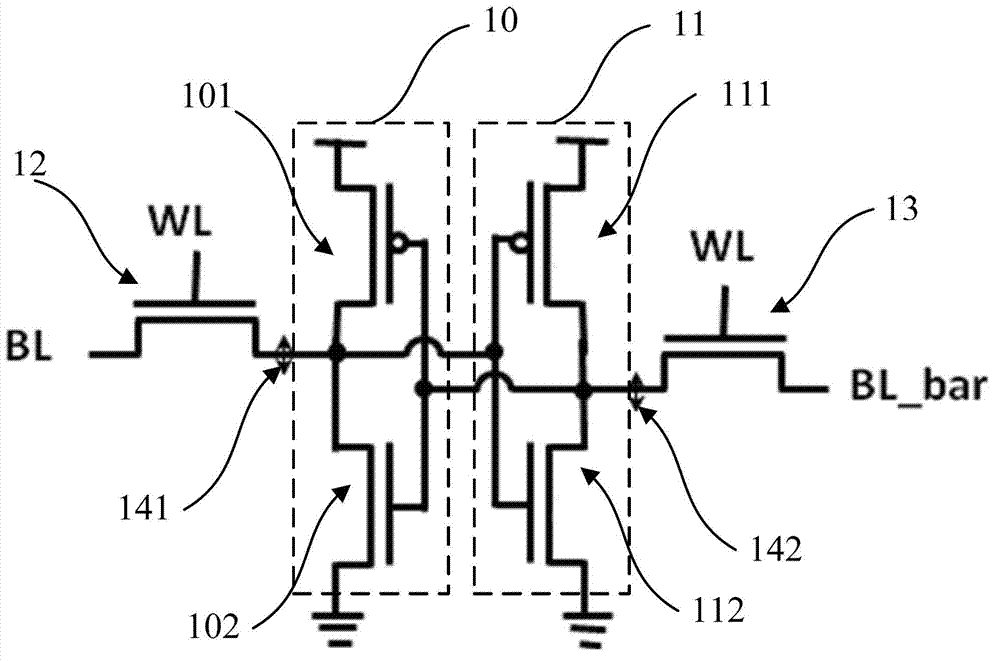

[0055] Such as Figure 1~Figure 3 As shown, the present invention provides a six-transistor SRAM unit, the memory unit at least includes:

[0056] The first inverter 10 is composed of a first PMOS transistor 101 and a first NMOS transistor 102;

[0057] The second inverter 11 is composed of a second PMOS transistor 111 and a second NMOS transistor 112;

[0058] The transmission gate is composed of a third NMOS transistor 12 and a fourth NMOS transistor 13;

[0059] Wherein, the source of the third NMOS transistor 12 is connected to the output terminal of the first inverter 10 and the input terminal of the second inverter 11 at the same time, the gate is connected to the word line of the memory, and the drain is connected to the memory the bit line;

[0060] The source of the fourth NMOS transistor 13 is connected to the input terminal of the first inverter 10 and the output terminal of the second inverter 11 at the same time, the gate is connected to the word line of the me...

Embodiment 2

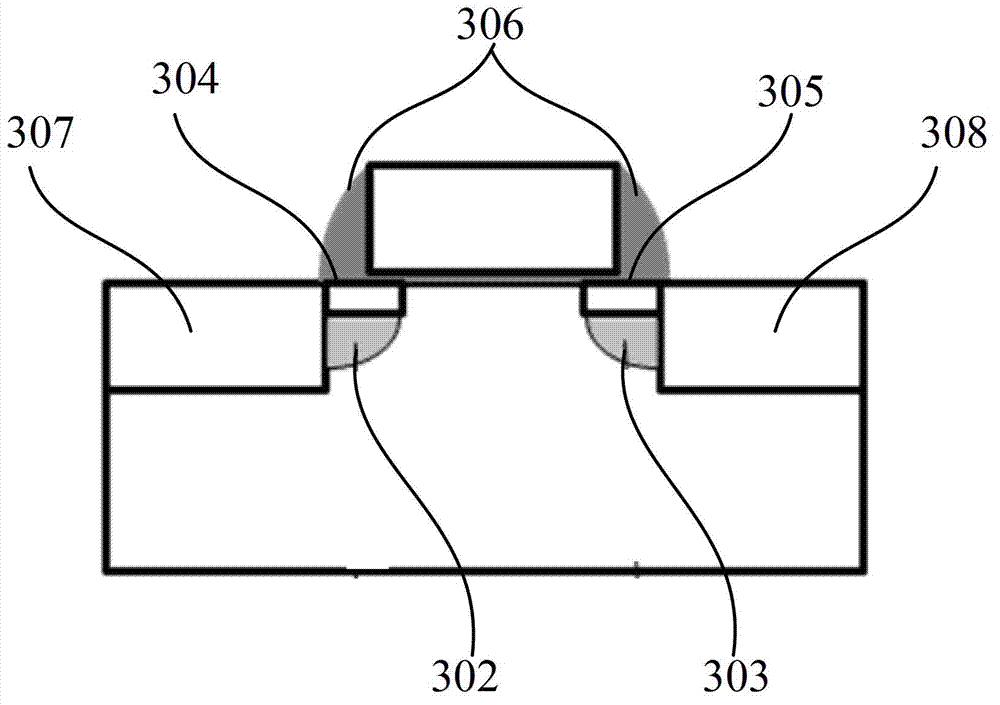

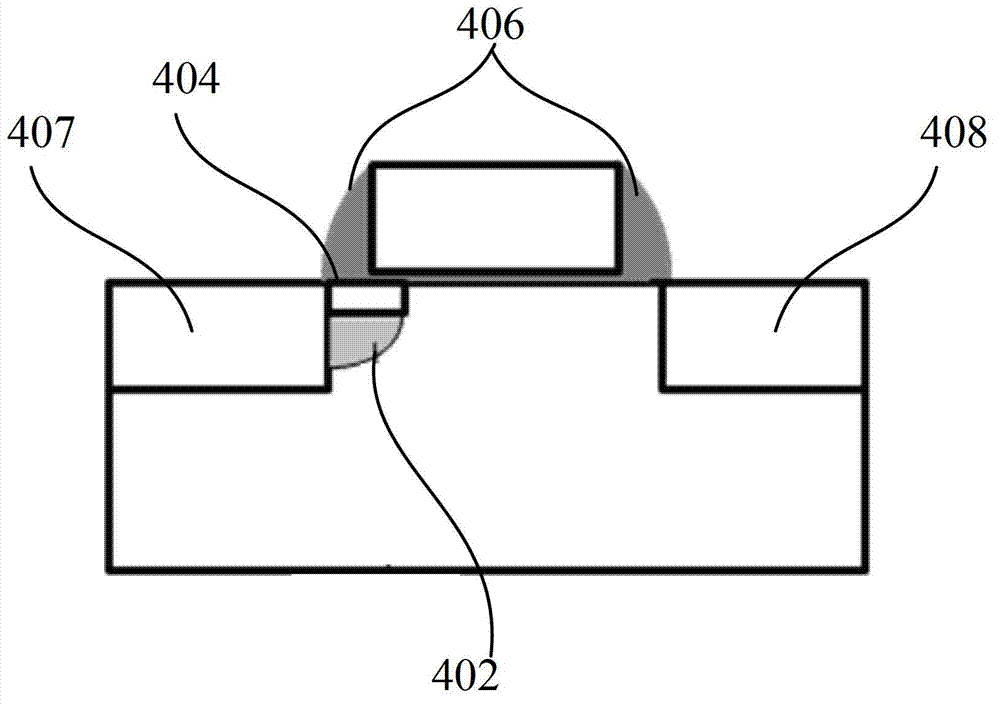

[0068] see Figure 2~3 and Figure 4~7 This embodiment provides a method for manufacturing a six-transistor SRAM unit, and the method at least includes the following steps:

[0069] Such as Figure 4 As shown, step 1) is first performed, providing a semiconductor substrate, and defining active regions 20a, 20b, 20c and 20d in the semiconductor substrate, and forming shallow trench isolation trenches around the active region ( not shown); specifically, the active regions 20a, 20b, 20c and 20d are defined first, then shallow trenches are etched around the active regions, and finally insulating materials are filled in the shallow trenches to form the Shallow trench isolation trenches. In this embodiment, the semiconductor substrate is a bulk silicon substrate or a silicon-on-insulator substrate, and the insulating material is silicon dioxide.

[0070] Such as Figure 5 shown, and then proceed to step 2) to form an N-type well implantation region 22 in the semiconductor subst...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com