High-speed single-selection multiplexer based on CMOS (Complementary Metal-Oxide-Semiconductor Transistor) process

A multiplexer and high-speed technology, applied in the field of high-speed multiplexer multiplexers, can solve the problems of high manufacturing cost and inability to meet integration needs, and achieve the effect of breaking through bandwidth limitations and obvious cost advantages.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

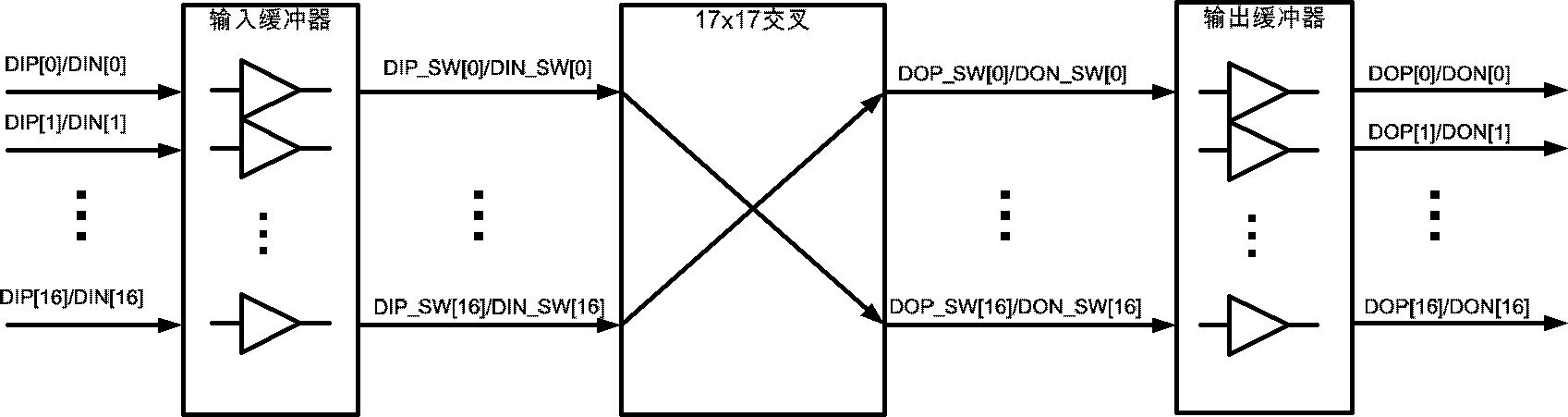

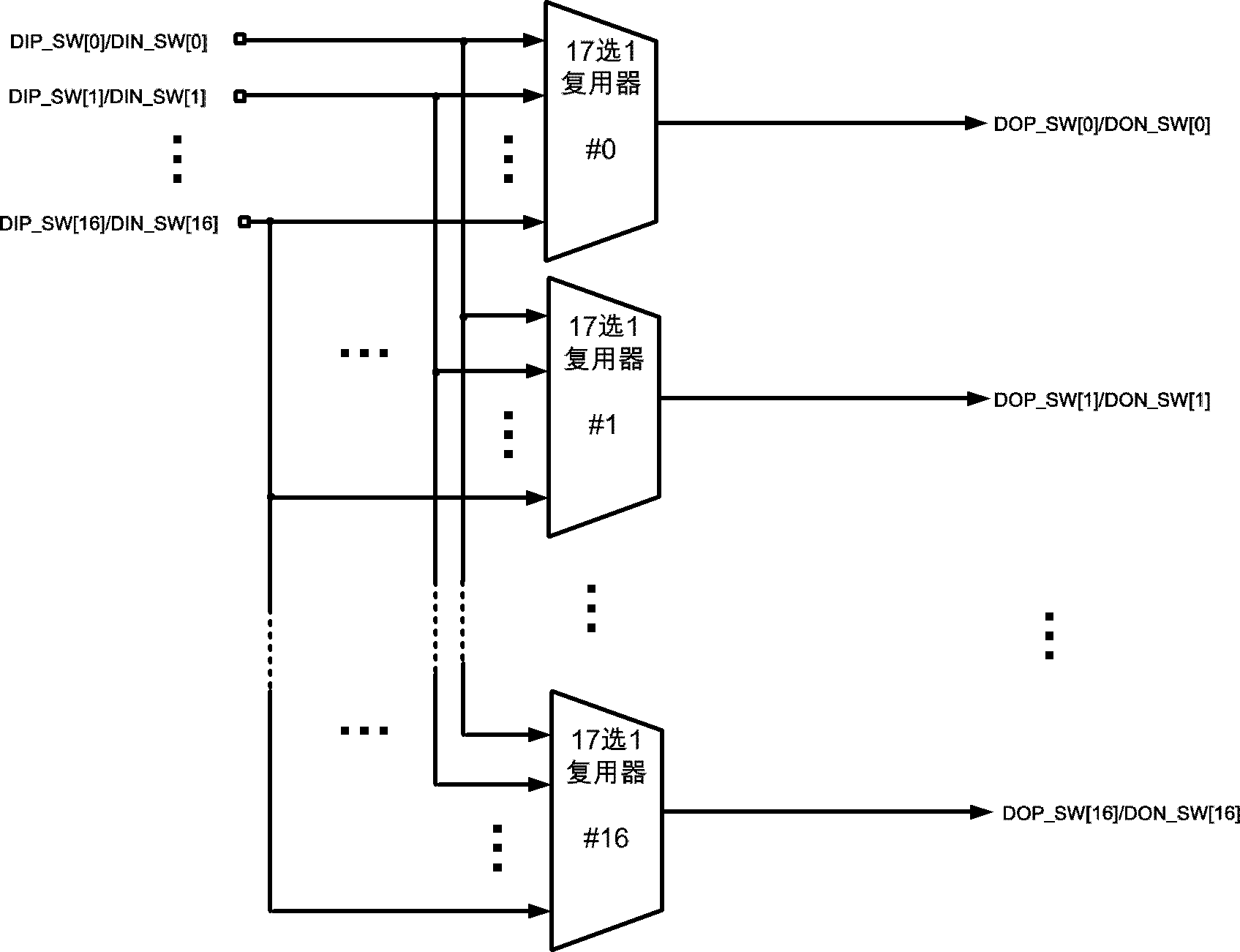

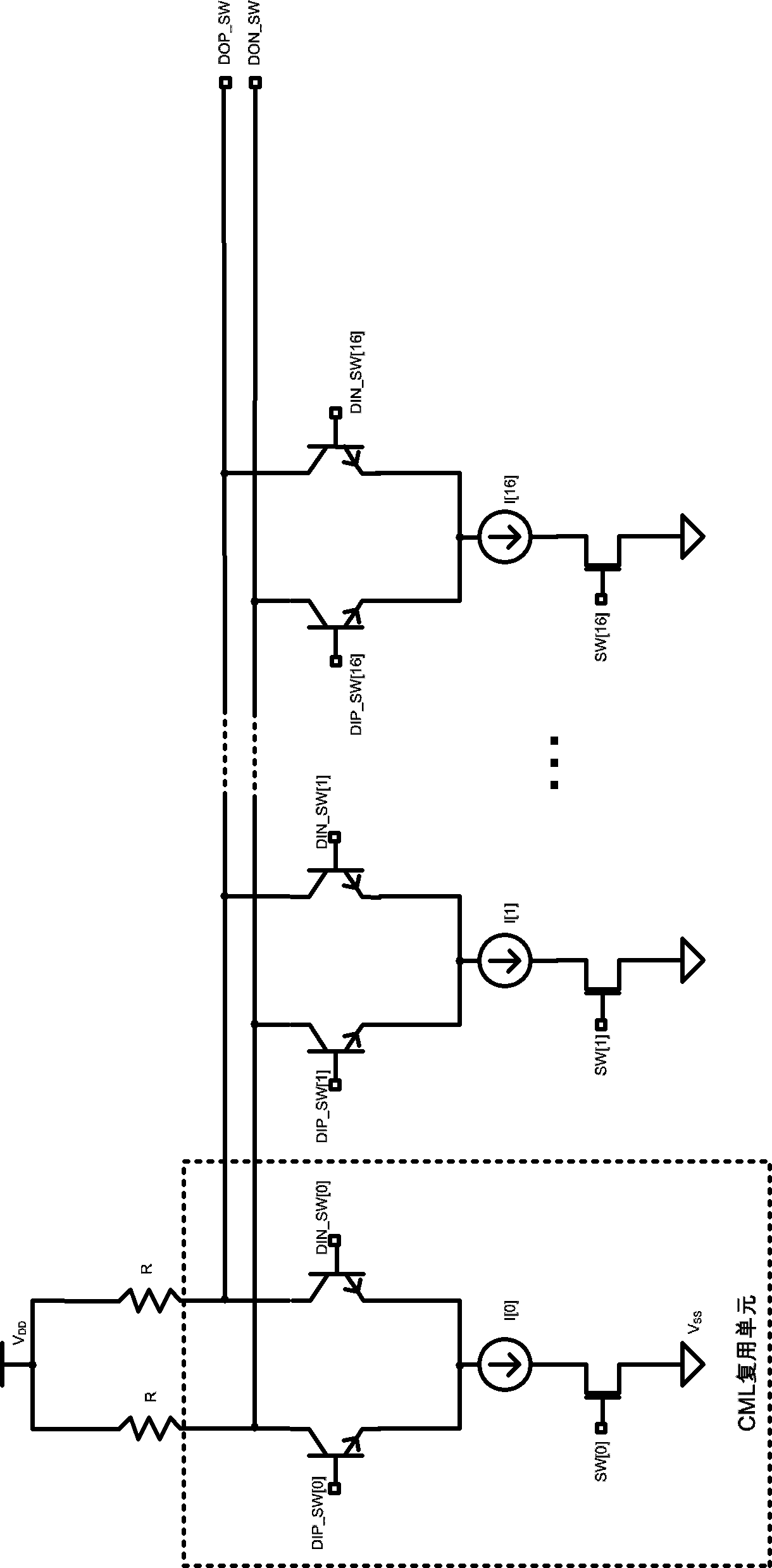

[0025] The invention provides a high-speed multi-choice multiplexer realized based on CMOS technology, which includes a plurality of CML multiplexer units and an equalizer.

[0026] Each CML multiplexing unit has a logic gating switch. When the logic gating switch in a certain CML multiplexing unit receives an enabling signal, the differential input signal input to the CML multiplexing unit is amplified as Corresponding differential amplifier output signal output;

[0027] The equalizer is composed of several cascaded equalization units and a CML buffer unit. The equalization unit receives the output signal of the differential amplification of the previous stage, and compensates the high-frequency signal components in it to eliminate the ISI (Inter-Symbol Interference, inter-symbol interference phenomenon. ) to output a balanced differential signal, and the CML buffer unit receives the balanced differential signal and performs shaping and amplification to output a differential...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com