Method for improving erasing speed of SONOS (Silicon Oxide Nitride Oxide Silicon) by utilizing strained silicon technology

A technology of erasing and writing speed and strained silicon, which is applied in the manufacturing of electrical components, electric solid-state devices, semiconductor/solid-state devices, etc., can solve the problem of low hot electron injection programming efficiency, etc., to improve programming efficiency and speed, energy valley scattering probability The effect of reducing, reducing the effective mass

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. The specific embodiments described here are only used to explain the present invention, and are not used to limit the protection scope of the present invention.

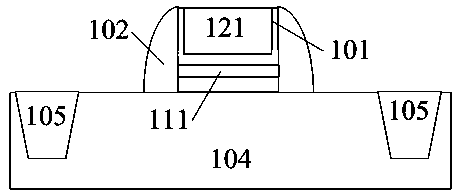

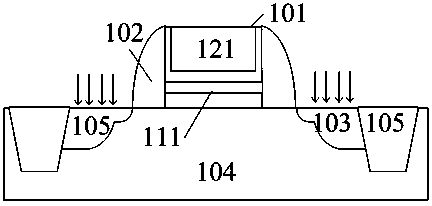

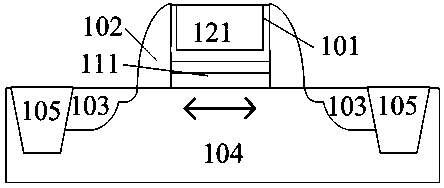

[0025] combined reference figure 1 and figure 2 , revealing the method of the present invention to improve the erasing and writing speed of SONOS by utilizing the strained silicon technology, figure 1 In the process, after forming the sidewall 102 of the gate 101 on the P-type substrate 104 with several shallow trench isolation regions 105 formed, the following steps are also included:

[0026] Step 1, precipitation barrier layer ( figure 1 not shown) covering the transistor;

[0027] Step 2, etch and remove the barrier layer covering the NMOS region to expose the NMOS region. In this step, first spin-coat photoresist on the barrier layer, and then perform photolithograph...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com