Chemical mechanical planarization method and manufacturing method of gate last

A planarization method and chemical-mechanical technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as process obstacles, drop, device short-circuit, etc., and achieve the effect of avoiding short-circuit defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] Figure 5 It is a flow chart of the chemical mechanical planarization method in this embodiment, Figure 6 to Figure 8 It is a schematic diagram of the chemical mechanical planarization method in this embodiment.

[0045] As shown, the method includes:

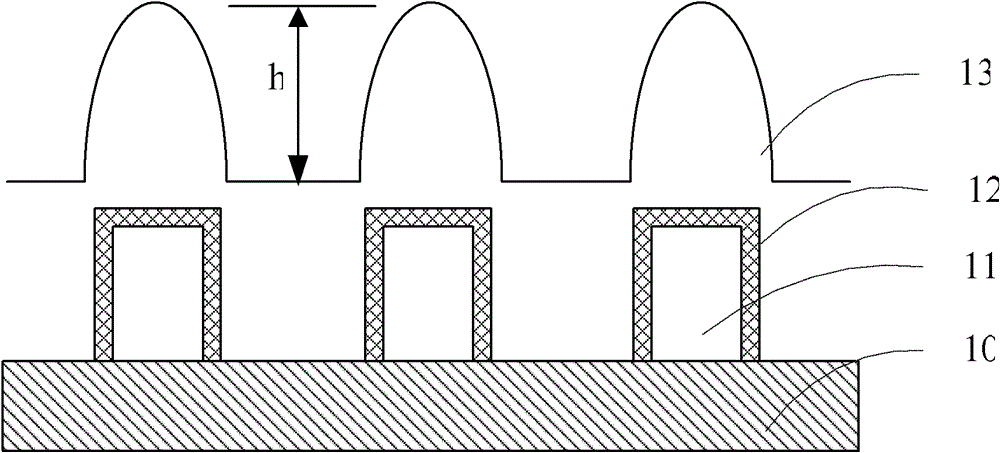

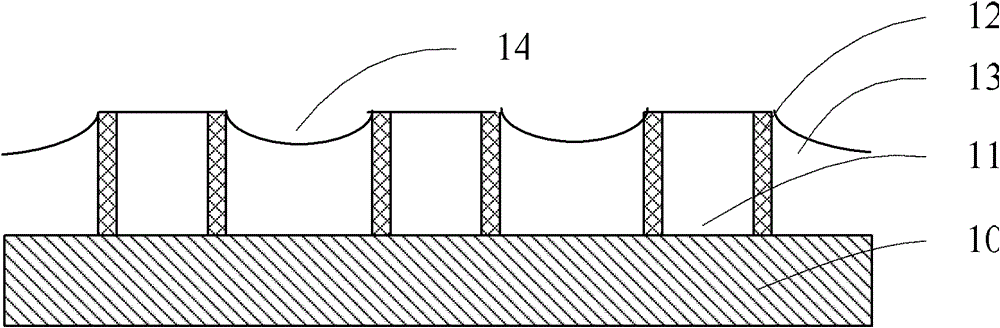

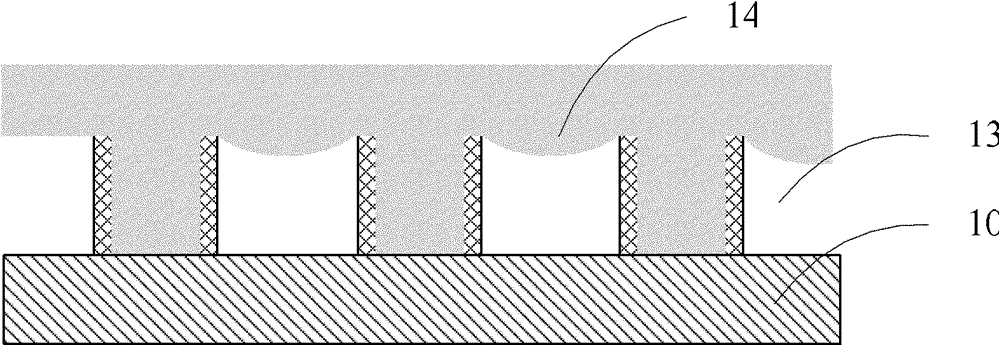

[0046] Step S1: if Figure 6As shown, a substrate 100 with a gate 101 and source and drain regions (not shown) on both sides of the gate 101 is provided, and the gate 101 and the source and drain regions are covered with an isolation layer 102, wherein the isolation layer 102 includes a raised portion 102a located above the gates and a recessed portion 102b located on the surface of the substrate between the gates 101 .

[0047] Step S2: Perform a selective doping process on the isolation layer 102, so that only the raised portion 102a is doped; preferably, in this embodiment, the selective doping process is an ion implantation process, refer to Figure 6 , the mask layer 103 covers the recessed portion 102b of the ...

Embodiment 2

[0055] This embodiment takes a typical metal gate-last manufacturing method of 32nm technology as an example to illustrate another implementation of the chemical mechanical planarization method. Figure 9 to Figure 16 It is a schematic diagram of the manufacturing method of the rear metal grid in this embodiment.

[0056] Such as Figure 9 As shown, a substrate 200 is provided. The substrate 200 includes a dummy gate 201, a gate oxide layer (not shown in the figure) and source and drain regions (not shown in the figure) on both sides of the dummy gate 200. The dummy gate 201 and The source and drain regions are sequentially covered with a first isolation layer 208 and a second isolation layer 202 .

[0057] Specifically, the substrate 200 can be a bulk material composed of elemental semiconductors or components, such as silicon or silicon germanium with a single crystal, polycrystalline or amorphous structure, or a bulk material composed of compound semiconductors, such as si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com