Low-power-consumption short pulse generation circuit and low-power-consumption pulse type D trigger

A technology for generating circuits and low power consumption. It is applied in the field of short pulse generating circuits. It can solve the problems of increasing power consumption of circuit transistors, increasing circuit power consumption, and increasing the number of circuit transistors, so as to reduce circuit power consumption, reduce the number of transistors, The effect of simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

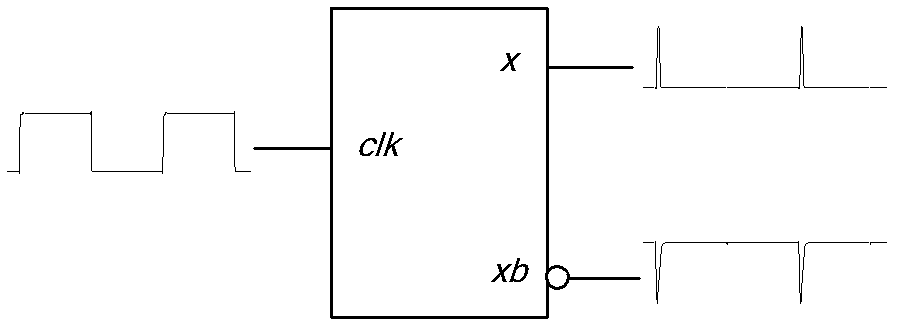

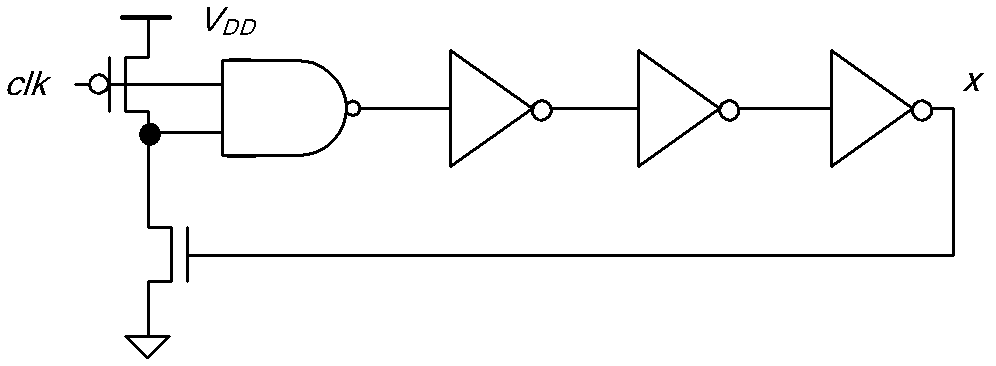

[0025] Embodiment one: if Figure 5 and Figure 6 As shown, a low-power short pulse generation circuit includes a first PMOS transistor P1, a first NMOS transistor N1, a first NAND gate U1 and a first inverter I1, the source of the first PMOS transistor P1 and the power supply Positive terminal V DD The first signal input terminal of the first NAND gate U1, the drain of the first PMOS transistor P1 and the drain of the first NMOS transistor N1 are connected, and the second signal input terminal of the first NAND gate U1 Connected to the gate of the first PMOS transistor P1, the source of the first NMOS transistor N1 is grounded, the signal output terminal of the first NAND gate U1, the signal input terminal of the first inverter I1 and the complementary pulse signal output terminal xb The three are connected, the signal output end of the first inverter I1, the gate of the first NMOS transistor N1 and the pulse signal output x are connected, the gate of the first PMOS transis...

Embodiment 2

[0026] Embodiment 2: other parts are the same as Embodiment 1, the difference is: the channel length of the second PMOS transistor P2, the channel length of the third PMOS transistor P3, the channel length of the second NMOS transistor N2 and the third The channel length of the NMOS transistor N3 is 1.3 times of the minimum channel length under the PTM90nm standard process.

Embodiment 3

[0027] Embodiment 3: other parts are the same as Embodiment 1, the difference is: the channel length of the second PMOS transistor P2, the channel length of the third PMOS transistor P3, the channel length of the second NMOS transistor N2 and the third The channel length of the NMOS transistor N3 is 1.4 times the minimum channel length under the PTM45nm standard process.

[0028] The working principle of the low power consumption short pulse generating circuit of the present invention is as follows:

[0029] When the clock signal clk=0, the first PMOS transistor P1 is turned on, the drain of the first PMOS transistor P1 is charged to a high level, the first NAND gate U1 outputs the signal xb=1, and the first inverter I1 outputs the signal x= 0, the first NMOS transistor N1 is turned off.

[0030] When the clock signal clk=1, the first PMOS transistor P1 is closed, and the drain of the first PMOS transistor P1 is suspended. Since the drain of the first PMOS transistor P1 is ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com