A kind of semiconductor power device and its manufacturing method

A technology for power devices and semiconductors, which is used in the manufacture of semiconductor/solid-state devices, semiconductor devices, transistors, etc., and can solve the problem of increased possibility of channel region punch-through under drain-source reverse bias and reduced channel region doping concentration, etc. problem, to achieve the effect of low Rds, lower Rds, and higher breakdown voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] The invention is explained in more detail below with reference to the accompanying drawings, in which preferred embodiments of the invention are shown. The present invention can be embodied in different ways and should not be limited to the embodiments described herein. For example, the description here refers more to N-channel MOSFET devices, but clearly other devices are also possible.

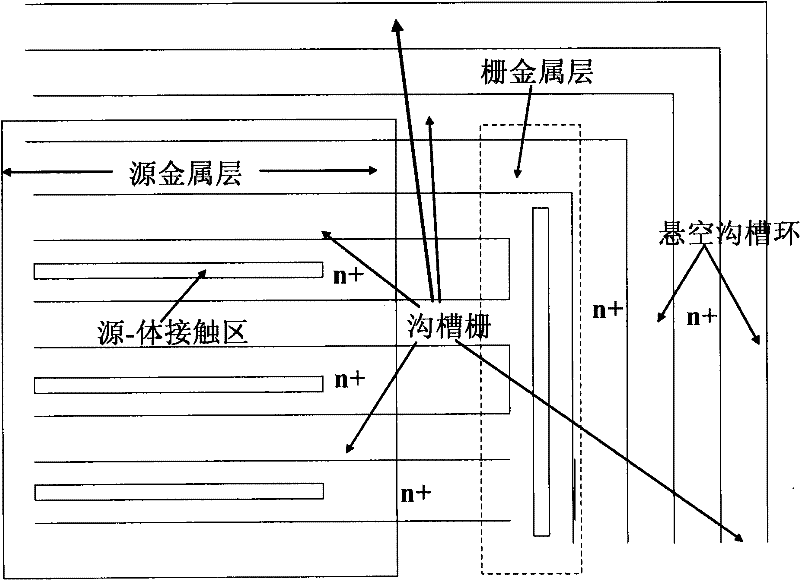

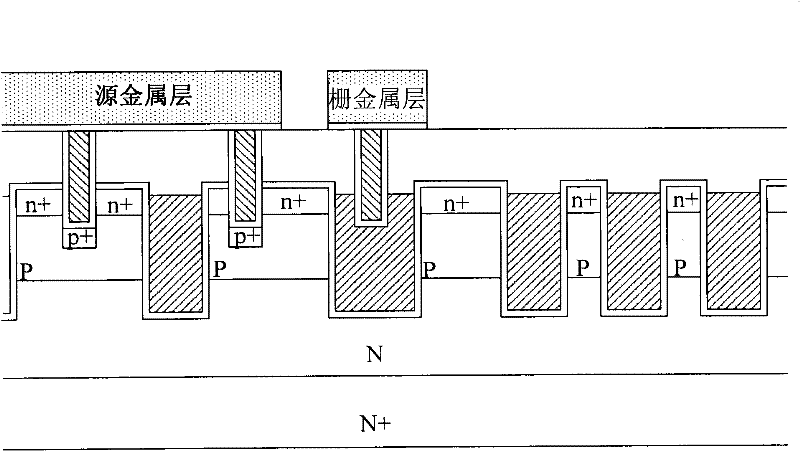

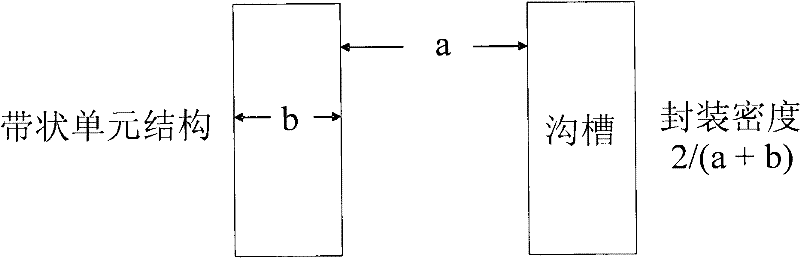

[0050] refer to Figure 2A and 2B A sectional view and a top view of a preferred embodiment according to the present invention are shown respectively. In this embodiment, an N-channel MOSFET device 100 is formed on an N+ substrate 105 and has an N-type epitaxial layer 110 . The MOSFET device includes a trench gate 120 within a trench whose inner surface is lined with a gate insulating layer 115 . The P-type body region 125 is located between the trench gates 120 , and the P-type body region 125 includes an N+ source region 130 close to the upper surface of the P-type body region 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com