Life Prediction Method of Pmosfet Device Negative Bias Temperature Instability

An instability and life prediction technology, applied in the direction of single semiconductor device testing, etc., can solve the problems of not considering the simultaneous application of voltage on the gate and drain, limiting the life of the device, and large devices, so as to save the cost of test equipment and failure time short effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

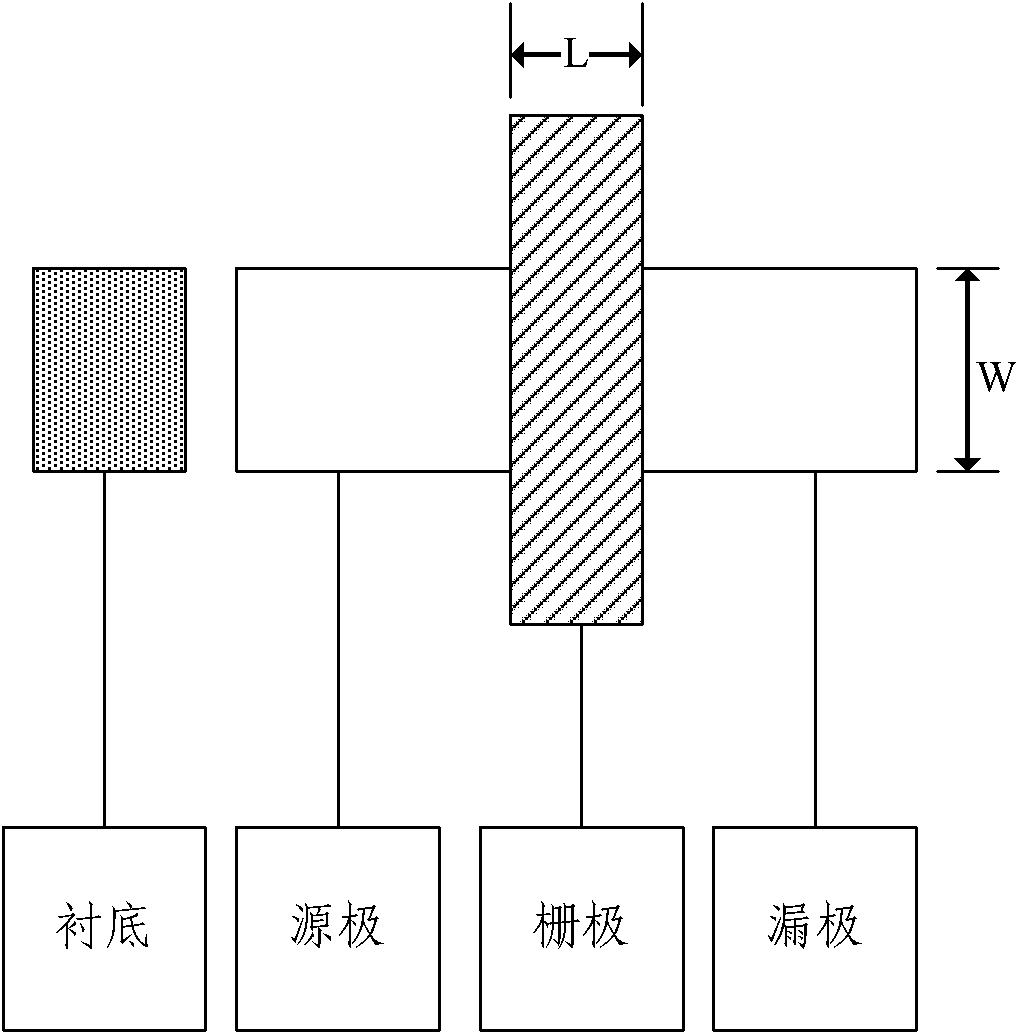

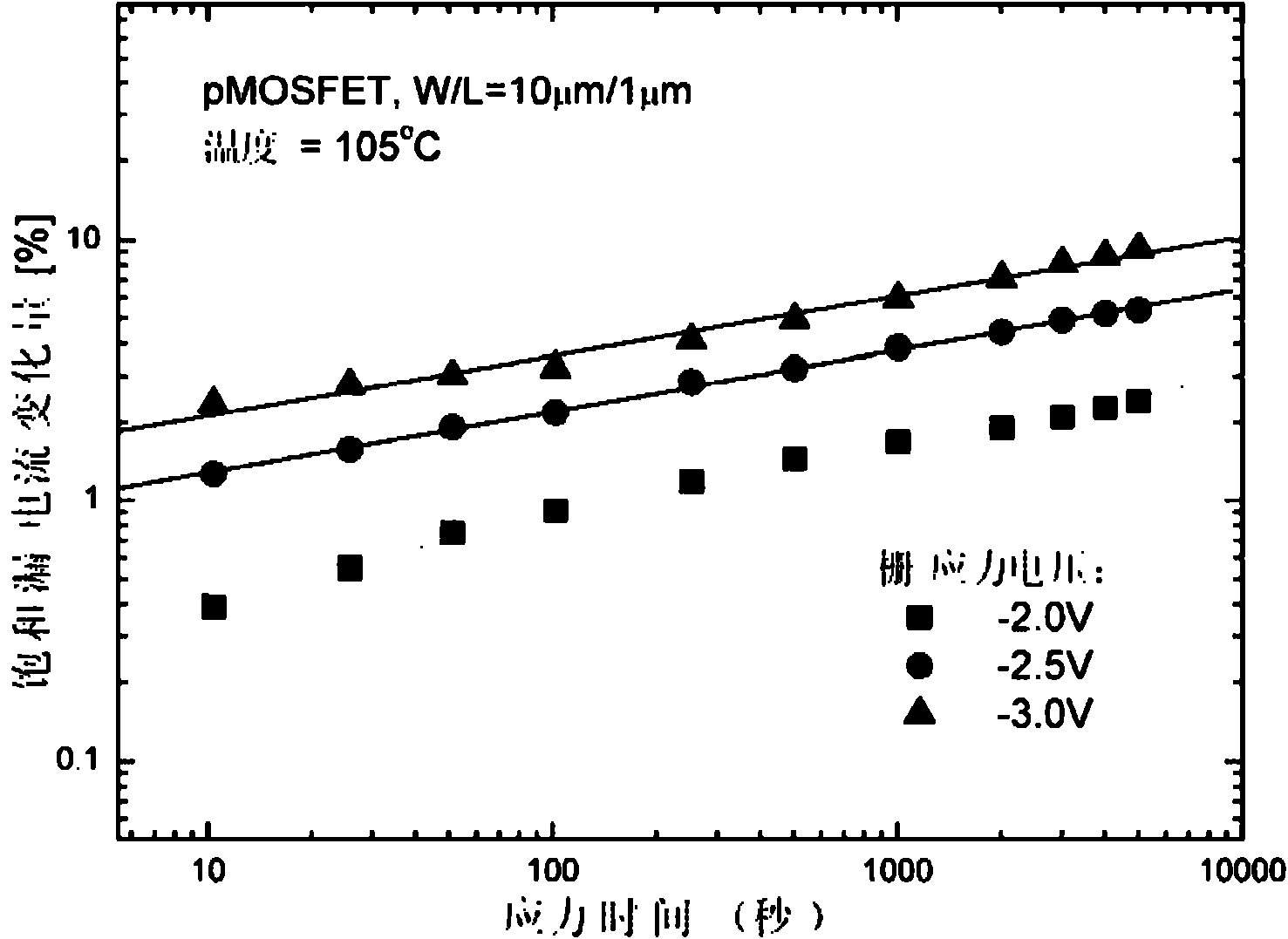

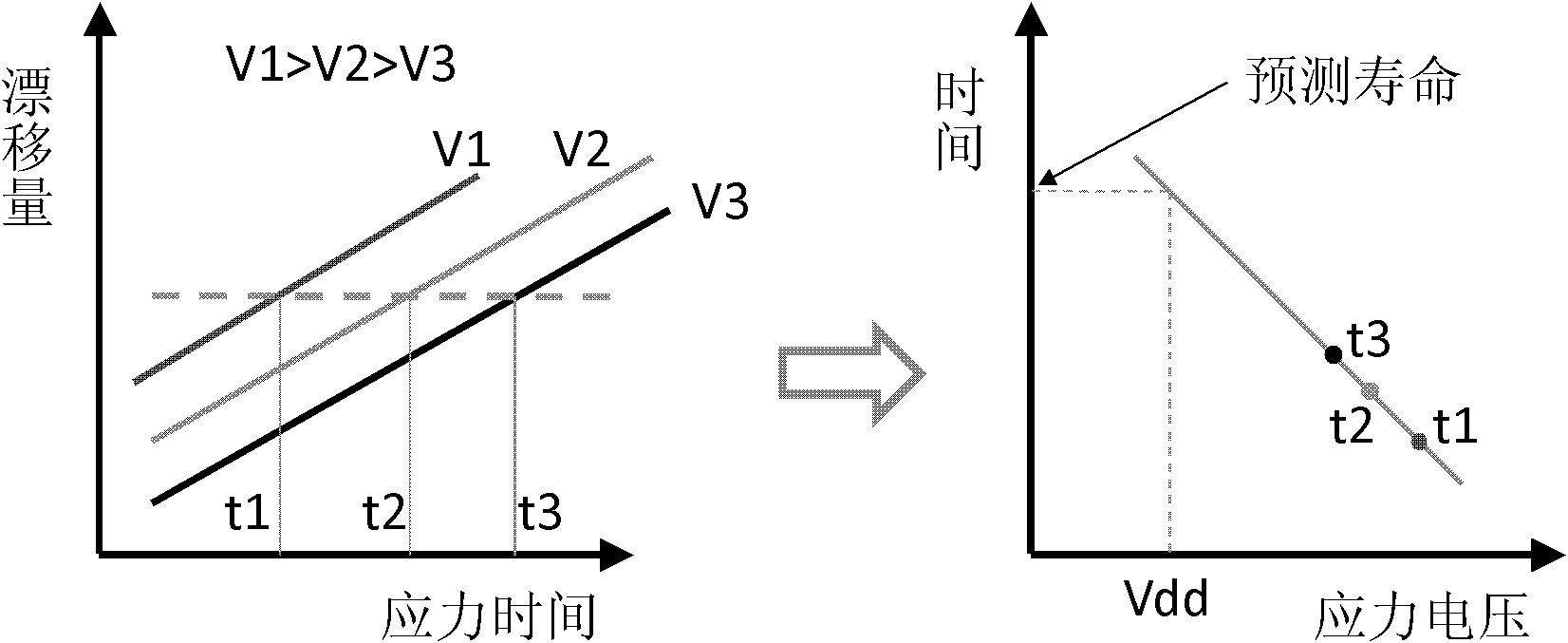

[0025] Starting from the bias state of the device in actual work, combined with the short-channel device structure, this patent proposes a method for predicting the lifetime of pMOSFET devices by applying a normal power supply voltage to the drain and accelerating stress through negative gate bias. This prediction method not only biases closer to the real working conditions of the device, but also under the same gate stress, the device failure time is shorter than the conventional method, so it can better reflect the NBTI life of the pMOSFET device. This approach employs short-channel device structures such as figure 1 As shown, where L is the shortest channel length, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com