Multicore architecture supporting dynamic binary translation

A technology of dynamic binary and architecture, applied in the direction of memory system, program control design, combination of various digital computers, etc., can solve the problems of low data access delay, small cache access conflict, high translation throughput, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

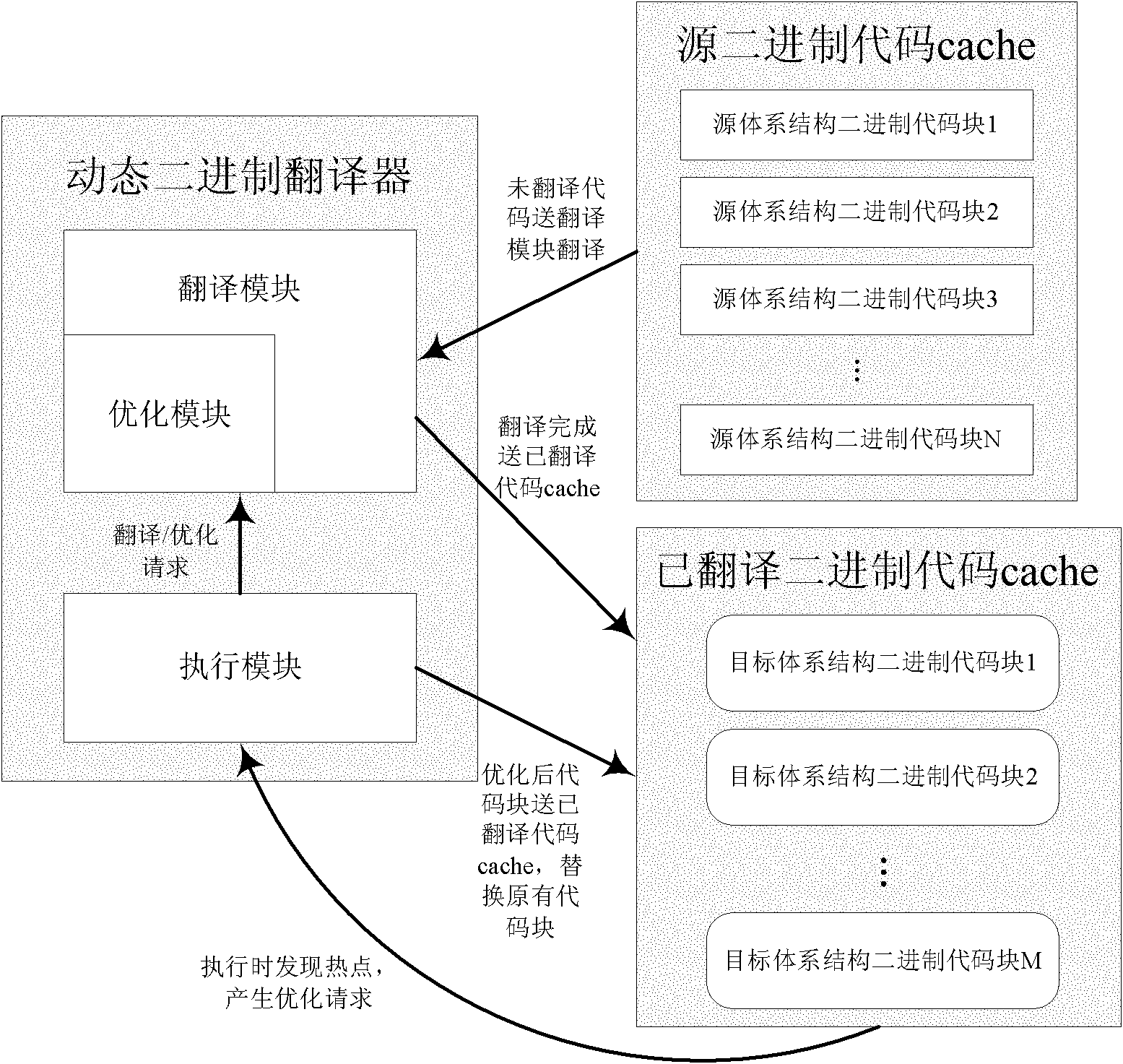

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

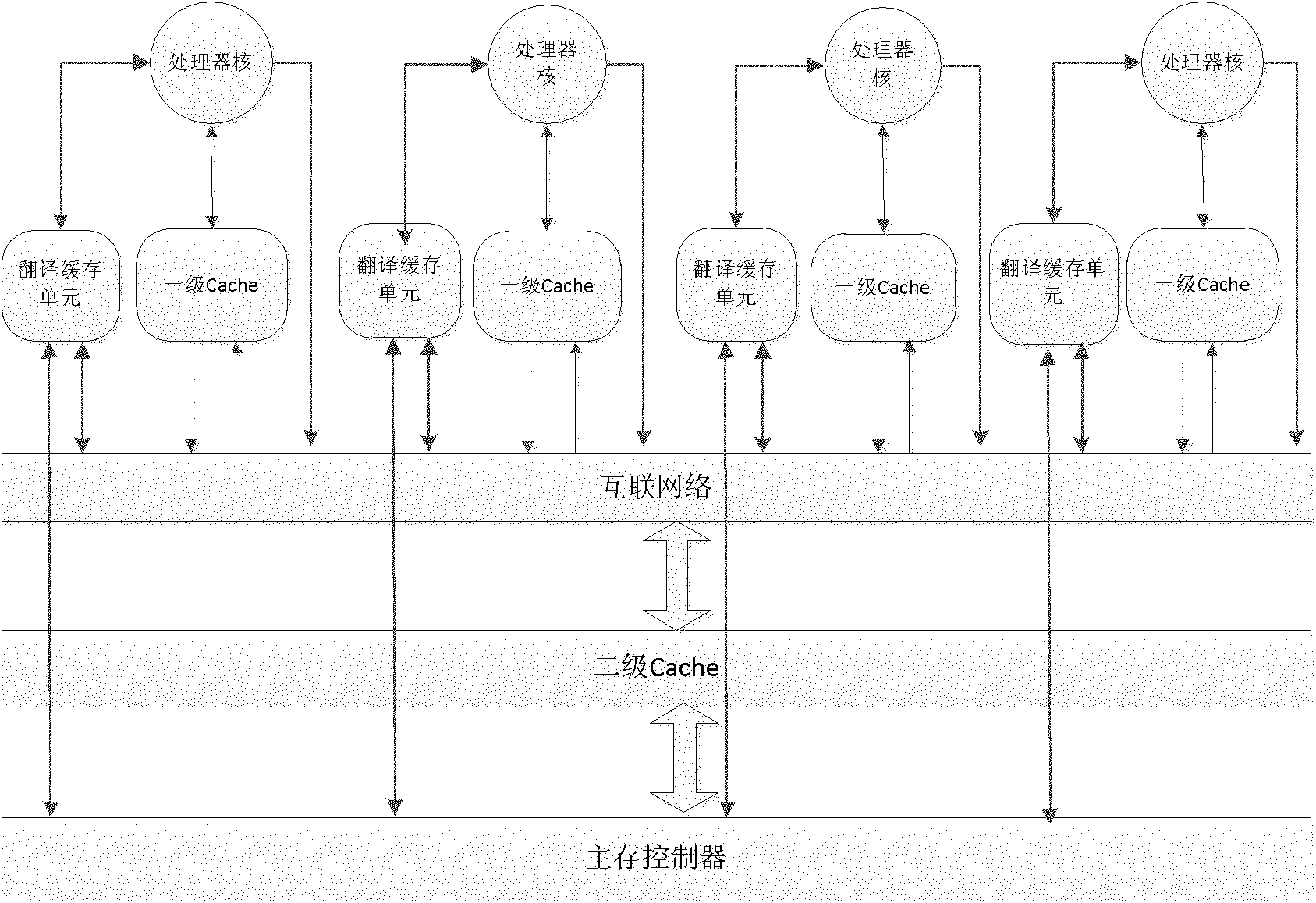

[0069] image 3 It is an overall logical structure diagram of the present invention. The multi-core architecture supporting dynamic binary translation consists of multiple processor cores, a first-level cache, a translation cache unit, a second-level cache, and a main memory controller. The first-level cache and translation cache unit are private to each processor core. The number of first-level cache and translation cache unit is the same as the number of processor cores. The second-level cache and main memory controller are shared by all processor cores. The translation cache unit is privately connected to its processor cores, inter-core communication interconnection network and main memory controller.

[0070] Figure 4 Translate the cache unit logic structure diagram for the present invention. The translation cache unit is composed of a communication control unit, a cache management unit, and a data storage unit. The data storage unit includes three storage areas, which...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com