Method for integrating copper and materials with low dielectric coefficient

A technology of low dielectric constant material and copper etching, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

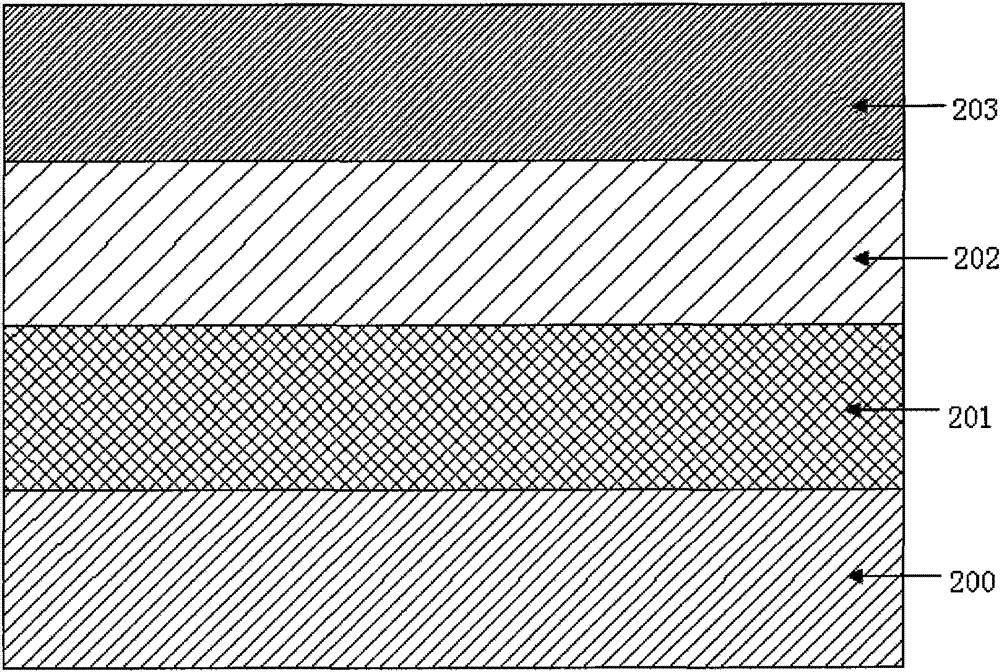

[0030] Step 1: Please refer to figure 1 , an integrated substrate 200 is provided, on which a thin film 201, a thin film 202 and a thin film 203 are sequentially formed, the substrate 200 is a silicon wafer or silicon oxide, the material of the thin film 201 is copper, the material of the thin film 202 is carbon, and the thin film 203 is photoresist layer.

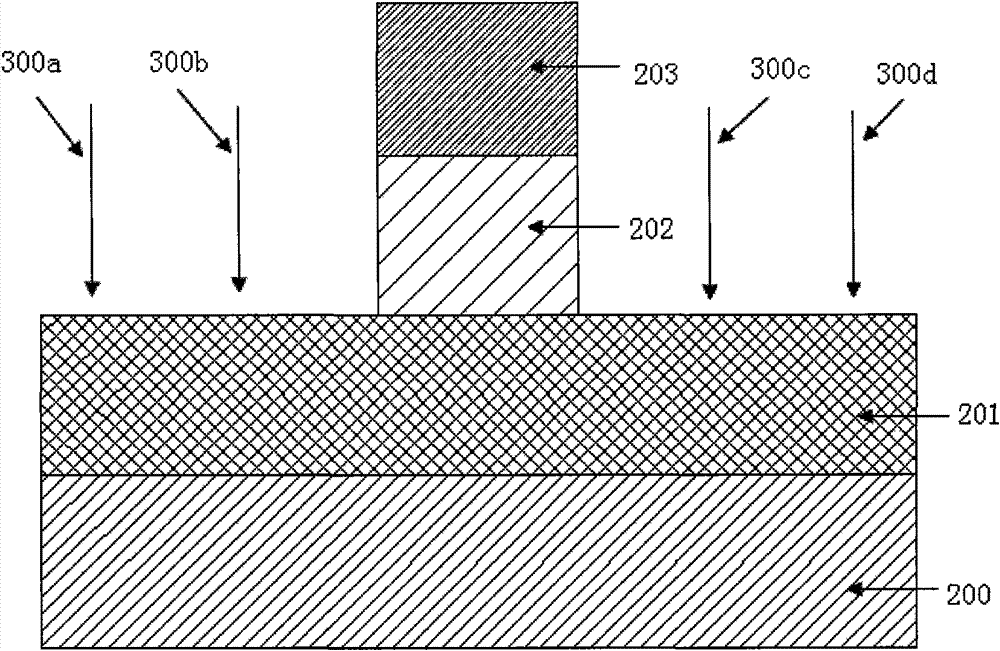

[0031] Step 2: Please refer to figure 2 , use photolithography technology and etching technology to etch the film 203 and film 202 according to the pattern, then immerse them in a solution containing hydrogen peroxide or ozone, and irradiate them vertically with light rays 300a, 300b, 300c and 300d, the light rays 300a, 300b , 300c and 300d are ultraviolet rays.

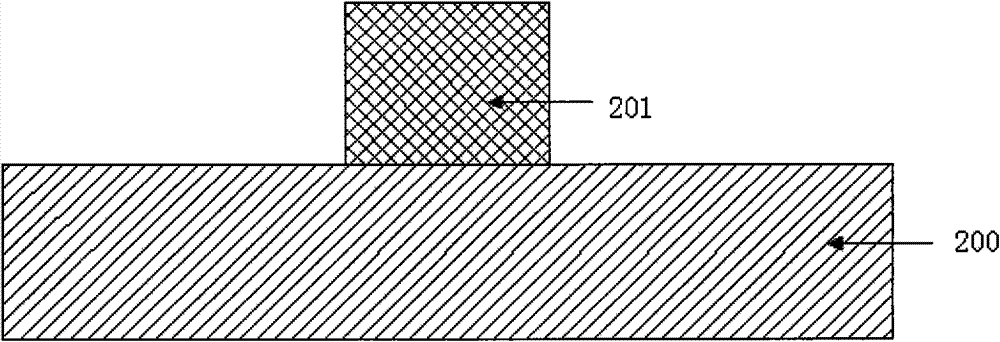

[0032] Step 3: Please refer to image 3 , etch the copper according to the pattern and remove the film 203 and the film 202 ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com