CMOS integrated circuit resisting total dose radiation

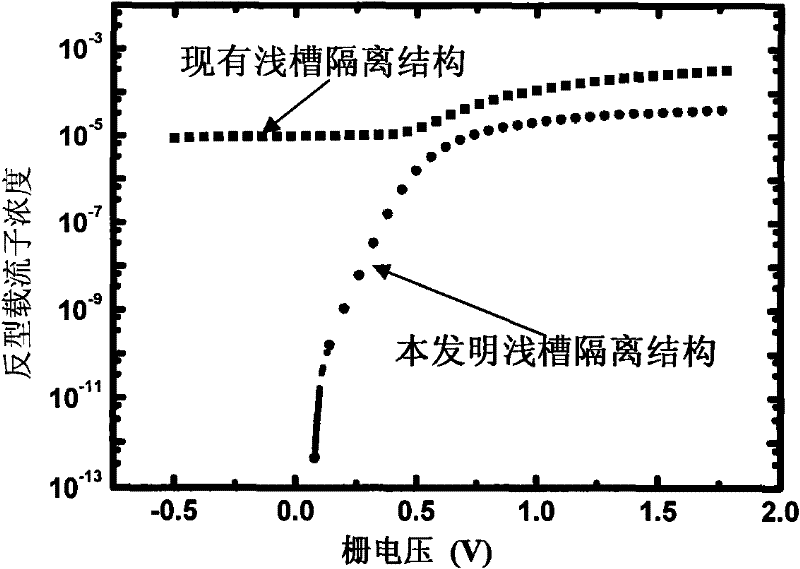

A total dose irradiation, integrated circuit technology, applied in the field of electronics, can solve the problems of increasing the power consumption of integrated circuits, large off-state leakage current, etc., to improve the total dose resistance performance, eliminate parasitic leakage, and improve the resistance to total dose irradiation. performance effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention will be further described below through a specific preparation example in conjunction with the accompanying drawings.

[0018] This embodiment prepares the CMOS integrated circuit of the present invention that is resistant to total dose irradiation of NMOS devices, mainly including the following steps:

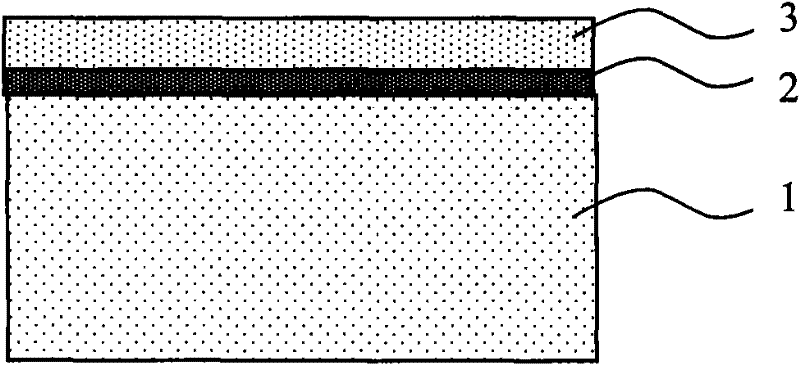

[0019] 1) Silicon dioxide and silicon nitride formation. Such as figure 2 shown. Thermally oxidize and grow a layer of silicon dioxide with a thickness of about 100 angstroms to 200 angstroms on the bulk silicon substrate 1 as a stress buffer layer 2 between silicon nitride and the silicon substrate, and then use low-pressure chemical vapor deposition (LPCVD) method to deposit a layer of 1000 angstrom to 1500 angstrom silicon nitride as the barrier layer 3 .

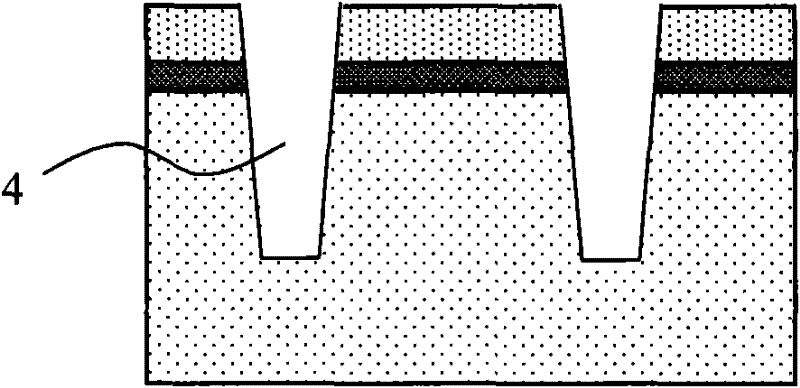

[0020] 2) Trench lithography and etching. Such as image 3 As shown, after defining the shown pattern by photolithography, the trapezoidal groove 4 is etched by reactive ion etching (RI...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com