Semiconductor package and manufacturing method thereof

A packaging and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as ineffective wetting, crack damage, moisture intrusion, etc., to avoid process steps and costs increased effect

Inactive Publication Date: 2010-12-01

SILICONWARE PRECISION IND CO LTD

View PDF9 Cites 0 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

However, in the aforementioned process, etching or cutting must be used to separate each of the first leads, which not only complicates the process but also increases the cost; moreover, cracks are prone to occur at the places where the first leads are etched or cut due to insufficient encapsulation. and the problem of moisture intrusion. In addition, the cross-section of the first lead pin at the etched or cut part is prone to oxidation, so that when the package is subsequently soldered to an external device using surface mount technology (SMT), the solder material cannot effectively wet it. In addition, when the arrangement density of the first pins is high, it is easy to cause the lower surface of the first pins to be covered by the encapsulation gel due to the overflow of glue when the package is molded. Additional de-glue work is required

Therefore, how to provide a low-cost lead-frame semiconductor package with multiple additional electrical input / output terminals (I / O) and its manufacturing method, while eliminating the need for etching, cutting and separation operations, and avoiding additional electrical Problems such as cracks, moisture intrusion, ineffective wetting, and glue overflow on the permanent input / output (I / O) are issues that the relevant industries need to solve urgently.

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

no. 1 example

no. 2 example

no. 3 example

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

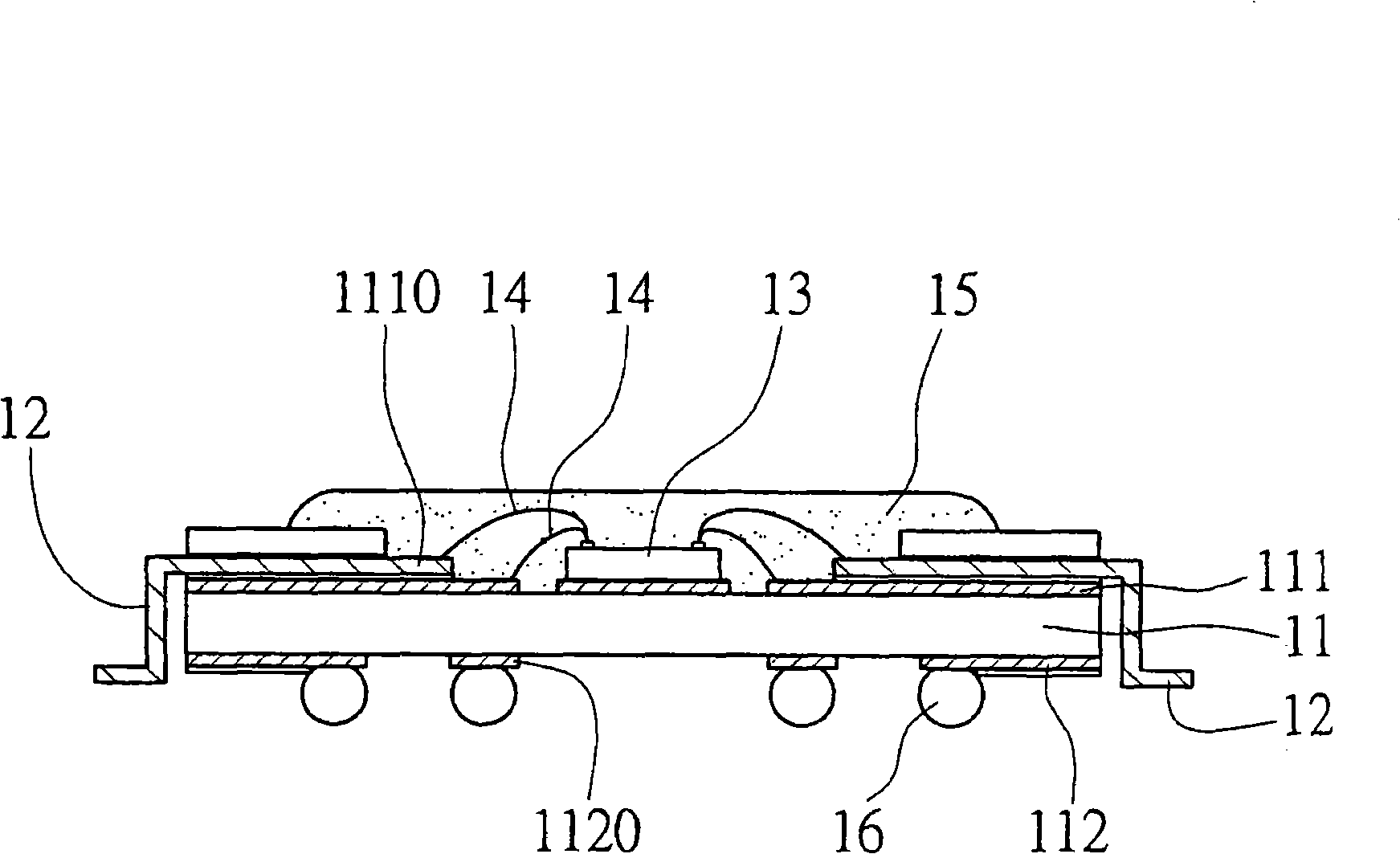

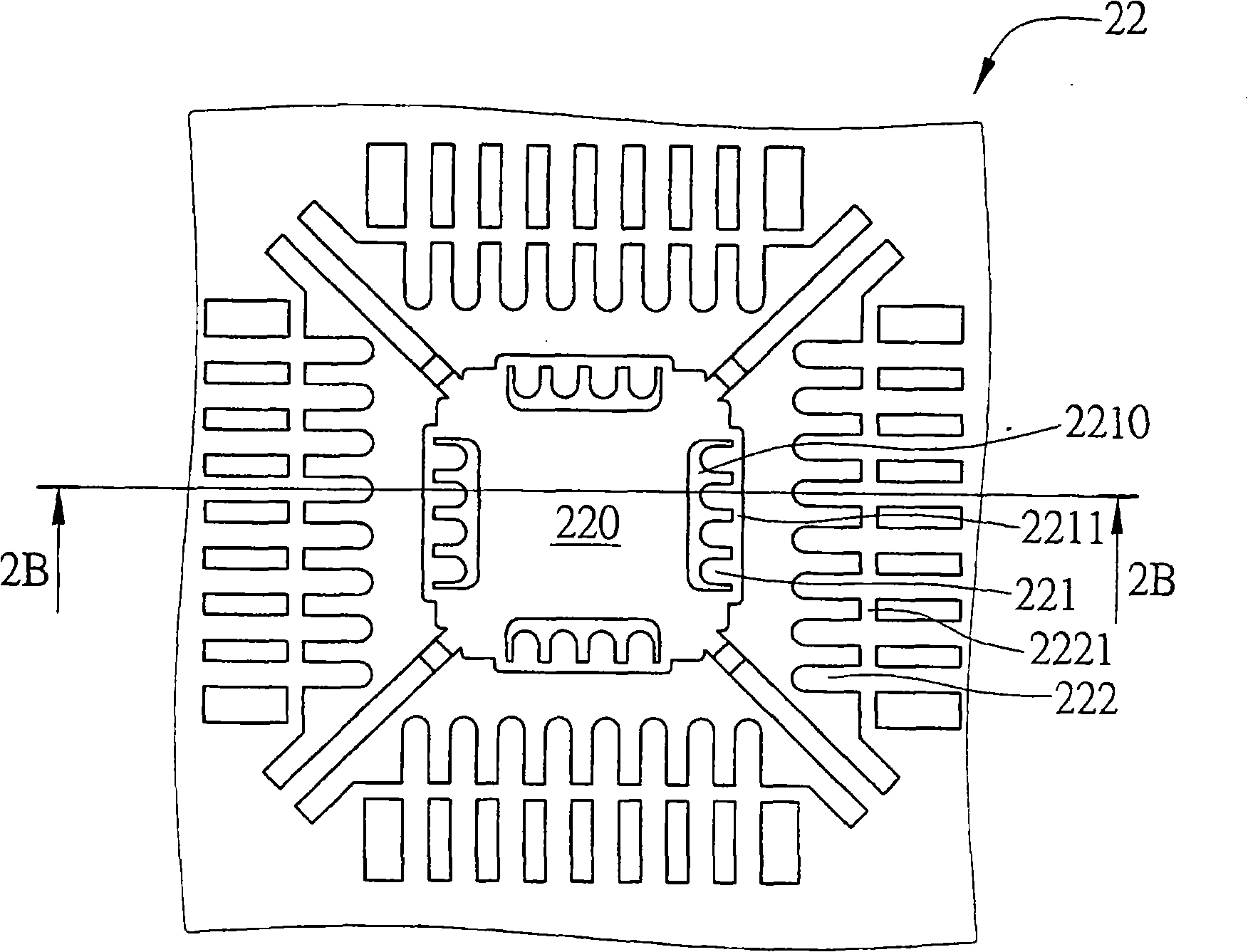

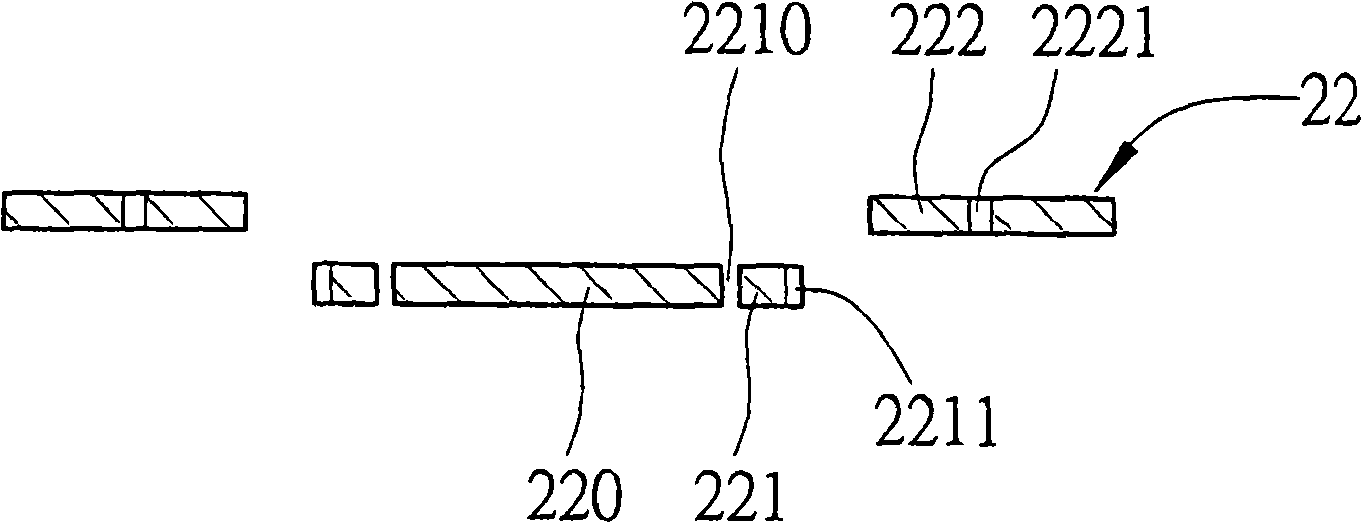

The invention discloses a semiconductor packaging part and a manufacturing method thereof. The semiconductor packaging part provides a carrier which is provided with a plurality of connecting pads on the surface so as to position the carrier on the lower surface of a lead frame chip holder correspondingly, wherein, the size of the carrier plane is more than the size of the chip holder plane so asto expose out of the connecting pad; at least one chip is arranged on the surface of the lead frame chip holder by connection, and the chip is connected with the carrier connecting pad and a lead frame foot by electricity with a multi-welding line, then an packaging colloid which covers the chip, the welding line, part of the carrier as well as the lead frame is formed, which leads the lower surface of the carrier and the foot to partially expose out of the packaging colloid, thereby increasing an electricity input / output (I / O) by the connecting pad of the carrier, solving the problem that glue overflow happens in an packaging molding press operation and complex processes are caused due to extra feet which are increasingly arranged in the chip holder in the prior, and avoiding the problemthat process steps and cost are increased as the separating operation of extra foot is conducted, and the problems of crack and loss, moisture intrusion and oxidation due to insufficient covering of the packaging part after the extra foot is separated.

Description

Semiconductor package and its manufacturing method technical field The invention relates to a semiconductor package and its manufacturing method, in particular to a lead frame type semiconductor package capable of adding electrical input / output terminals (I / O) and its manufacturing method. Background technique Traditional lead frame semiconductor packages, such as quad flat semiconductor packages (QuadFlatPackage, QFP), are manufactured by providing a lead frame with a die pad (DiePad) and a multi-lead (Lead), for the die pad Put a chip on it, and further electrically connect the pads (Pad) on the upper surface of the chip with the corresponding multi-lead pins through multi-wires (Wire), and wrap the chip and the wires with an encapsulant to form a wire rack type semiconductor package. The disadvantage of this traditional lead frame semiconductor package is that the pins used as electrical input / output terminals (I / O) can only be arranged around the periphery of the pac...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Patents(China)

IPC IPC(8): H01L21/50H01L21/60H01L21/56H01L23/488H01L23/495H01L23/31

CPCH01L2224/32245H01L2224/48091H01L2224/48227H01L2224/48247H01L2224/49109H01L2224/73265H01L2924/15311H01L2924/181H01L2924/00014H01L2924/00H01L2924/00012

Inventor 詹长岳黄致明李春源赖志兴

Owner SILICONWARE PRECISION IND CO LTD

Features

- Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com