Ion injection method of semiconductor device

An ion implantation and semiconductor technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of semiconductor device performance attenuation and lower yield, and achieve the effect of reducing attenuation and improving yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

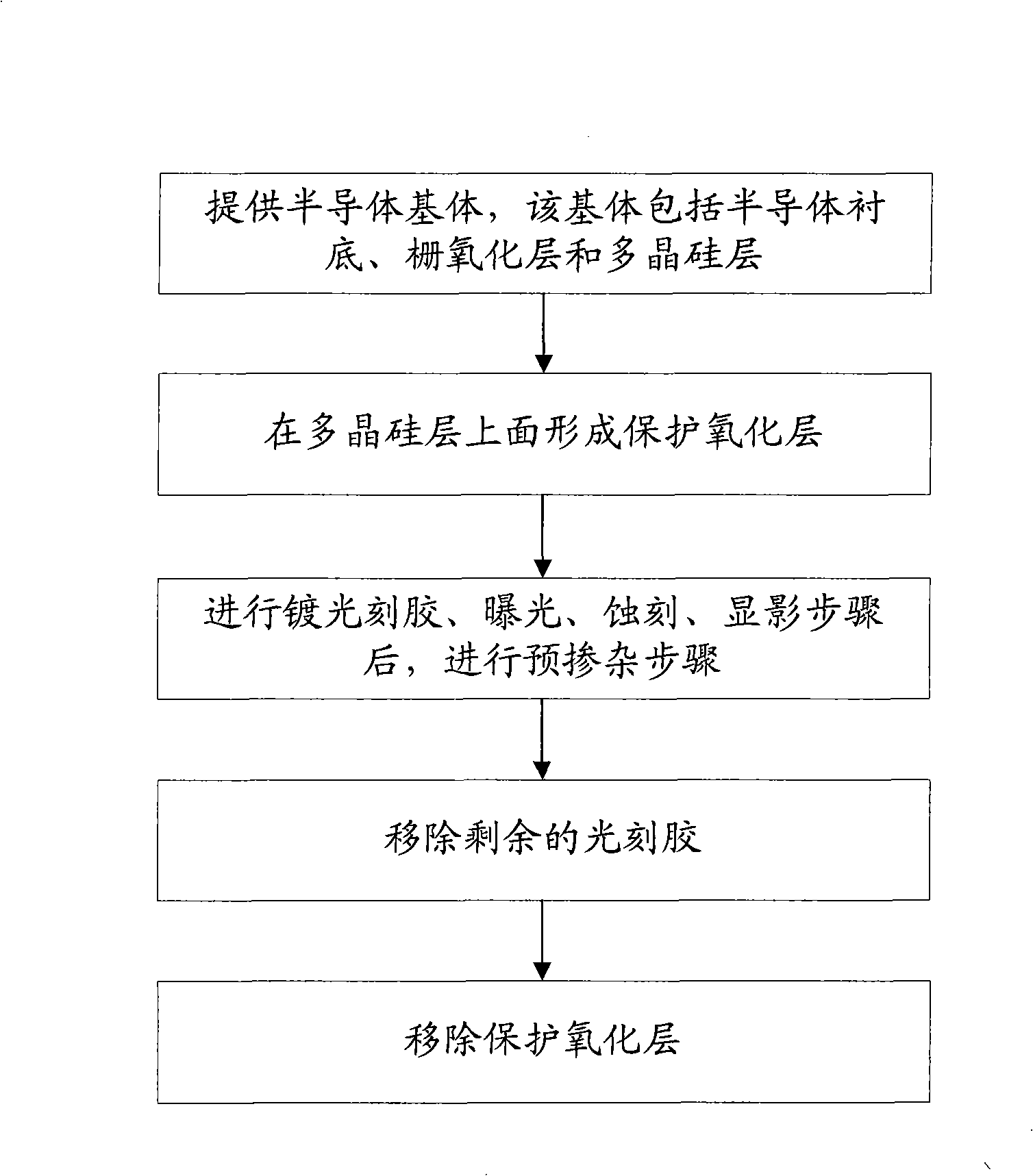

[0014] Combine below figure 1 The ion implantation method disclosed in the present invention is further described in detail.

[0015] The ion implantation method of the present invention comprises the following steps:

[0016] A semiconductor base is provided, which includes a semiconductor silicon substrate, a gate oxide layer deposited on the substrate, and a polysilicon layer deposited on the gate oxide layer as a gate of a semiconductor device;

[0017] A thin protective oxide layer is formed on the polysilicon layer. The protective oxide layer can be formed in a high-temperature furnace or in a rapid thermal oxidation system (rapid thermal oxidation, RTO), wherein the thickness of the protective oxide layer is The range is 20-100 Angstroms;

[0018] Plating a photoresist on the protective oxide layer can be based on the photoresist characteristics, plating a positive photoresist or a negative photoresist, and then performing exposure, etching, and developing steps at a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com