Semiconductor packaging member and method for fabricating the same

A semiconductor and packaging technology, applied in the field of semiconductor packaging and its manufacturing method, can solve problems such as the reliability of solder joint cracks, shorten the arc length of welding wires, and reduce fatigue life, so as to improve circuit layout and electrical connection quality, shortening the electrical connection path, and shortening the arc length of the welding wire

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

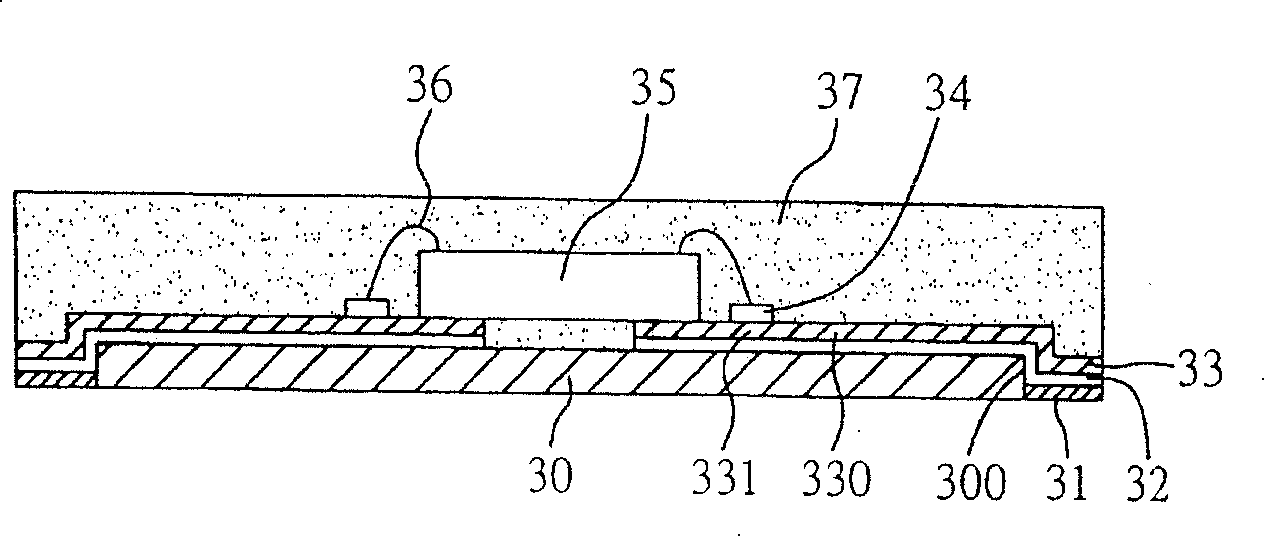

[0072] see Figures 4A to 4G , is a schematic cross-sectional view of the first embodiment of the semiconductor package and its manufacturing method of the present invention.

[0073] Such as Figure 4A As shown, at first, a metal carrier (Carrier) 40 such as a copper plate (Cu Plate) is prepared, and a sacrificial layer 41 is laid on one surface of the metal carrier 40, and the sacrificial layer 41 is, for example, polymer (polymer) It is made of materials, such as epoxy, photo-resist, etc., and its thickness is about 10 to 30 μm. The sacrificial layer 41 is formed by conventional methods of coating, exposure, development and etching, or by stencil printing to form the sacrificial layer 41 with a plurality of through openings 410 .

[0074] Such as Figure 4B As shown, an insulating layer 42 is laid on the surface of the sacrificial layer 41, and the insulating layer 42 is, for example, a solder mask (Solder Mask), and the insulating layer 42 is exposed by conventional coa...

no. 2 example

[0083] see Figure 5A and 5B , is a cross-sectional view of the second embodiment of the semiconductor package of the present invention. Such as Figure 5A As shown, the semiconductor package of this embodiment is roughly the same as the previous embodiment, the main difference is that the chip 58 of this embodiment is connected to the patterned circuit layer 55 in a flip-chip method (Flip-Chip); In other words, during the die bonding operation, the active surface of the chip 58 faces the patterned circuit layer 55 and is electrically connected to the terminal 550 of the patterned circuit layer 55 or the metal on the terminal 550 through a plurality of solder bumps 54 . layer 56 , and then form an encapsulant 59 covering the chip 58 . Compared with connecting the chip and the patterned circuit layer with bonding wires, the flip-chip technology using solder bumps can further shorten the electrical connection path between the chip and the patterned circuit layer, and can bett...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com