Windowing-type semiconductor packaging member and manufacture method thereof

A technology for semiconductors and packages, which is applied in the field of windowed semiconductor packages and its manufacturing methods, can solve the problems of shortening the arc length of welding wires, being unable to apply, reducing the electrical connection path between chips and conductive trace layers, etc., to achieve shortening The arc length of the welding wire, the improvement of the circuit layout and the quality of the electrical connection, and the effect of overcoming the short circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

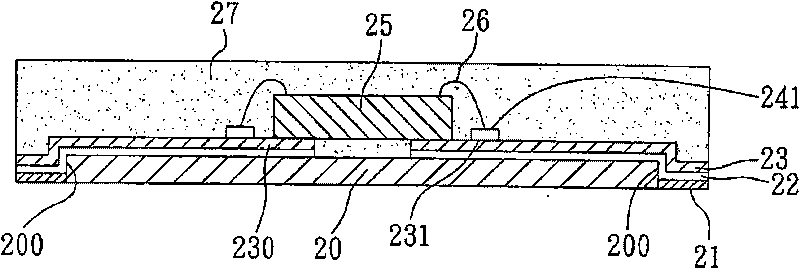

[0073] see Figure 3A to Figure 3K Shown is a schematic diagram of the first embodiment of the method for manufacturing a window-type semiconductor package of the present invention, wherein, Figure 3C for Figure 3B a schematic cross-section of the Figure 3G for Figure 3F sectional schematic diagram.

[0074] like Figure 3A to Figure 3C As shown, a metal (such as copper) base plate 310 is provided to form a dielectric layer 311 with a thickness of 50 to 100 microns (μm) on the metal base plate 310, and an exposed part of the metal is formed on the dielectric layer 311. The first opening 305 of the bottom plate 310 , and a plurality of first conductive vias 303 and second conductive vias 304 exposing part of the metal bottom plate 310 are formed on both sides of the first opening 305 .

[0075] like Figure 3D to Figure 3E As shown, the first conductive via 303 and the second conductive via 304 are filled with a conductive material 320 such as gold / nickel / copper (Au / N...

no. 2 example

[0085] see Figure 4A to Figure 4I Shown is a schematic diagram of the second embodiment of the method for manufacturing a window-type semiconductor package of the present invention, wherein, Figure 4C for Figure 4B a schematic cross-section of the Figure 4G for Figure 4F sectional schematic diagram. In addition, in order to simplify the drawings and facilitate understanding, elements corresponding to or similar to those in the foregoing embodiments are denoted by the same numbers. Furthermore, the manufacturing method of the window-type semiconductor package of this embodiment is substantially the same as that of the first embodiment, the main difference being that the first opening 305 can be formed on the dielectric substrate 300 by punching or laser cutting.

[0086] like Figure 4A to Figure 4C As shown, a metal base plate 310 is provided to form a dielectric layer 311 with a thickness of 50 to 100 microns (μm) on the metal base plate 310, and a plurality of firs...

no. 3 example

[0092] see also Figure 5A to Figure 5I , is a schematic diagram of the third embodiment of the manufacturing method of the window-type semiconductor package of the present invention, wherein, Figure 5B for Figure 5A a schematic cross-section of the Figure 5E for Figure 5D sectional schematic diagram. In addition, in order to simplify the drawings and facilitate understanding, elements corresponding to or similar to those in the foregoing embodiments are denoted by the same numbers. Furthermore, the manufacturing method of the window-type semiconductor package of this embodiment is substantially the same as that of the first embodiment, the main difference is that the conductive trace layer 330 of the dielectric carrier 300 is embedded in the dielectric carrier 300 .

[0093] like Figure 5A to Figure 5B As shown, a metal base plate (such as copper) 310 is provided, a resistive layer 332 is formed on the metal base plate 310 , and a plurality of third openings 335 exp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com