TFT LCD array substrate peripheral wiring structure and its producing method

A technology of array substrates and peripheral wiring, applied in semiconductor/solid-state device manufacturing, nonlinear optics, optics, etc., can solve problems such as large coupling effects, reduce overlapping areas, increase spatial distance, and reduce capacitive coupling effects Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

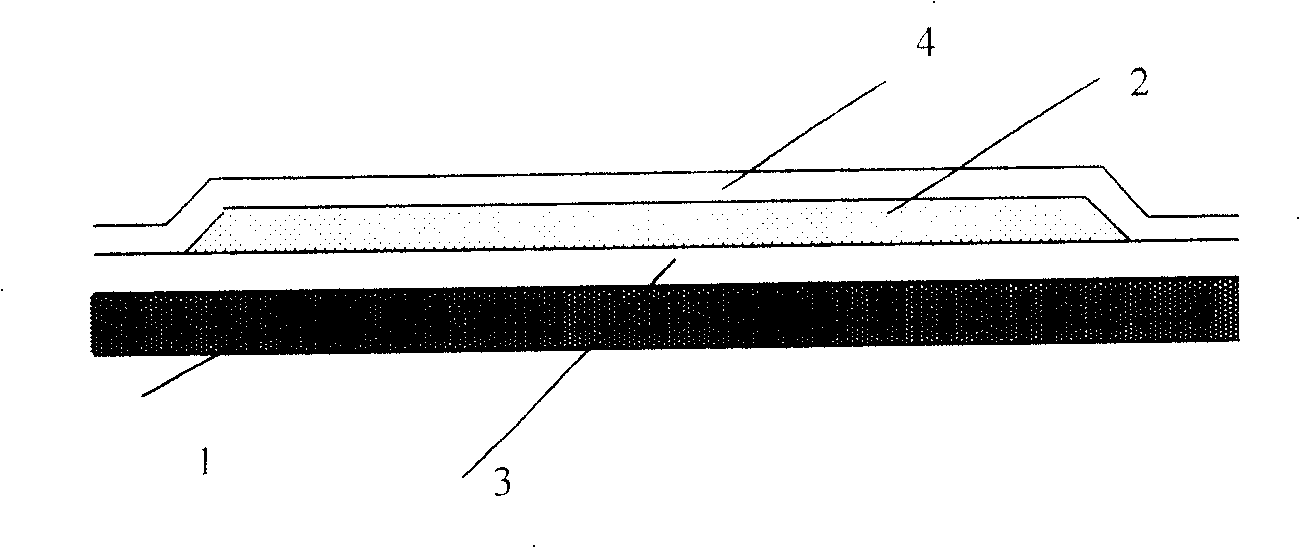

[0048] Figure 4 It is a top view of the structure of the outer common electrode wiring and the repair line in the TFT outer overlapping area of a specific embodiment of the present invention, Figure 4 The cross-sectional view of the C-C position and the D-D position in the middle is as follows Figure 5 and Figure 6 shown. Such as Figure 4 As shown, the structure includes: a TFT substrate (including an array substrate); a set of repair lines 1, generally two, or multiple; a layer of gate insulating layer 3 formed on the repair line 1 The peripheral common electrode wiring 2 is formed on the gate insulating layer 3 and overlaps with the repair line 1 ; the passivation layer 4 is formed on the peripheral common electrode wiring 2 . Wherein, the materials of the repair wire 1 and the peripheral common electrode wire 2 can be one or any combination of molybdenum, aluminum, aluminum-nickel alloy, molybdenum-tungsten alloy, chromium, or copper.

[0049] Such as Figure 4...

Embodiment 2

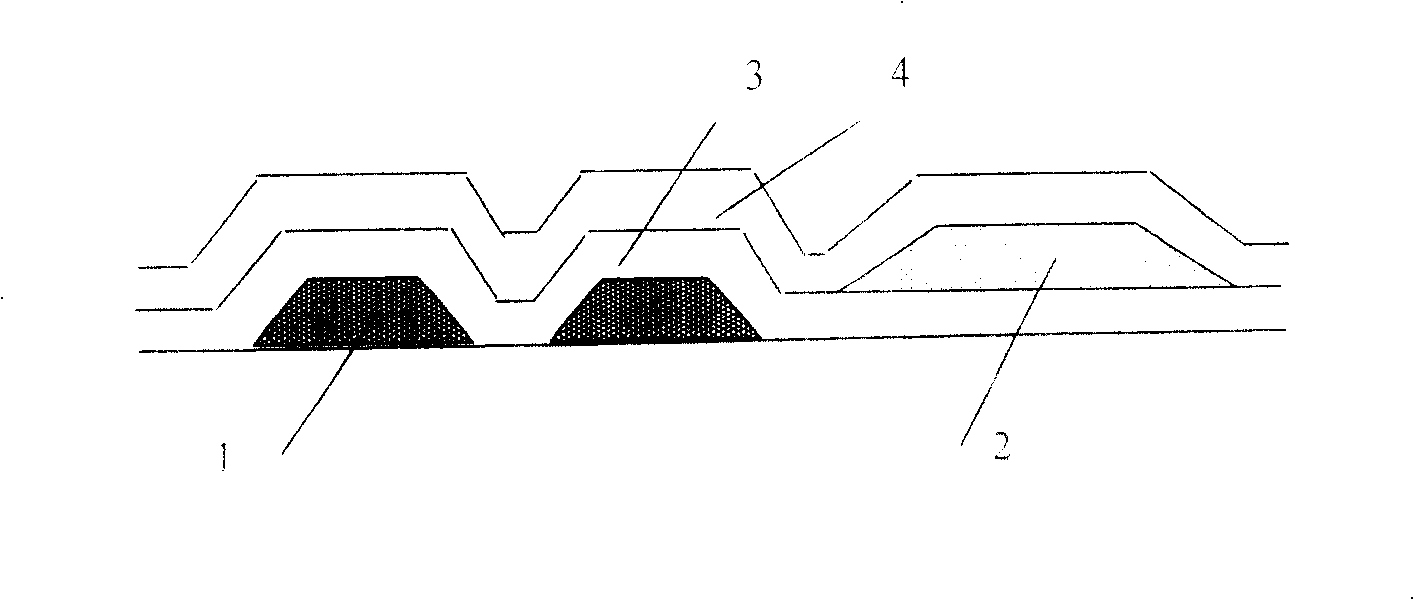

[0058] Figure 7 It is a top view of the outer common electrode wiring and the repair line in the TFT outer overlapping area of another specific embodiment of the present invention, Figure 7 The cross-sectional views of the E-E position and the F-F position in the middle are as follows Figure 8 and Figure 9 shown. Such as Figure 7 As shown, the structure includes: a TFT substrate (including an array substrate); a set of repair lines 1, usually two, or multiple; a gate insulating layer 3, formed on the repair line 1; The electrode wiring 2 is formed on the gate insulating layer 3 and disconnected at the position above the repair line 1; the passivation layer 4 is formed on the peripheral common electrode wiring 2 and is close to the peripheral common electrode wiring 2 A passivation layer via hole or groove 6 is formed at the disconnected position; a connecting lead 5 is formed on the passivation layer 4 and connects the disconnected peripheral common electrode wiring...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com