Dielectric etch method with high source and low bombardment plasma providing high etch rates

A plasma and etching technology, applied in the fields of plasma, chemical instruments and methods, semiconductor/solid-state device manufacturing, etc., can solve problems such as component deformation and production yield decline

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

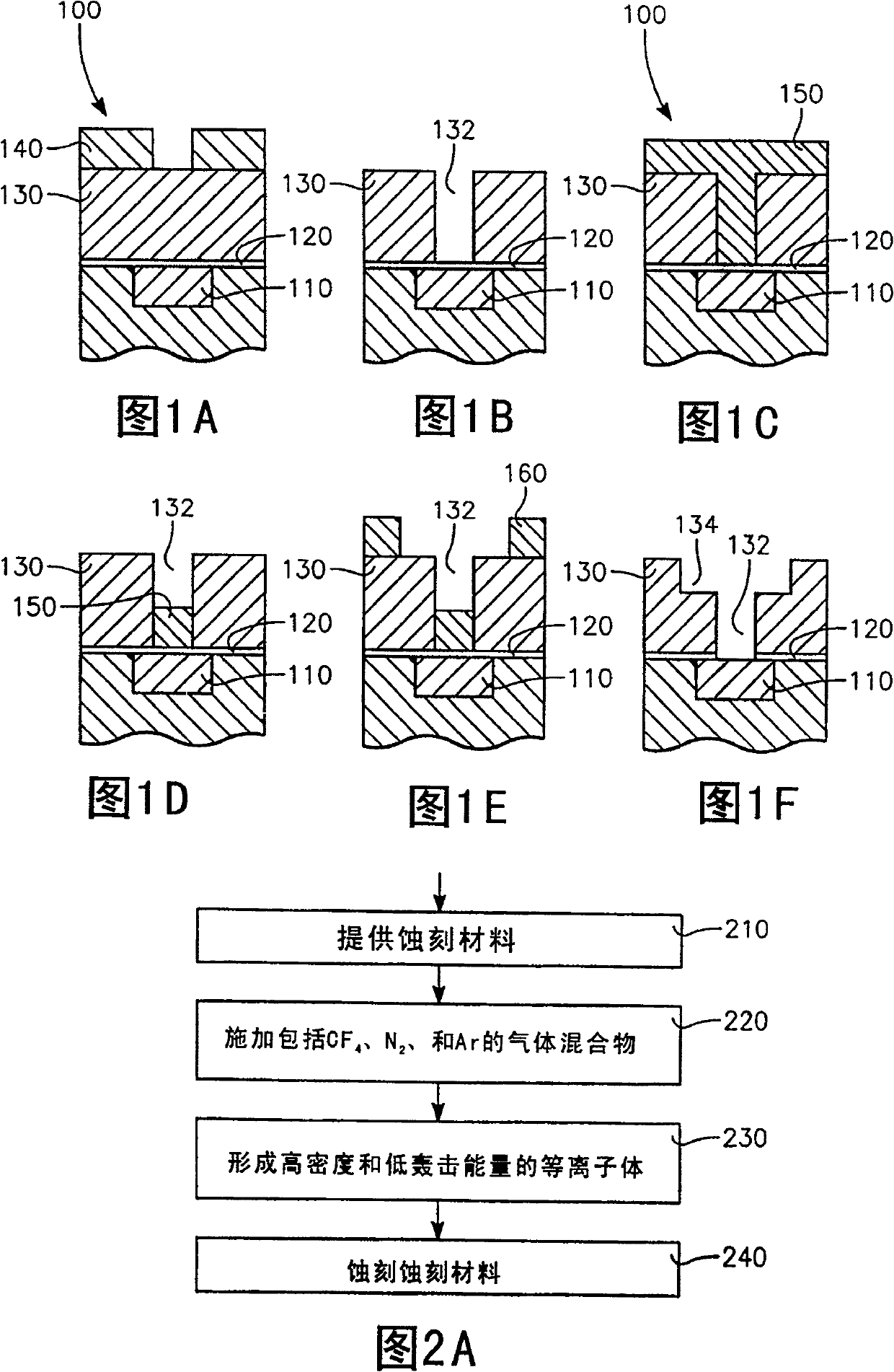

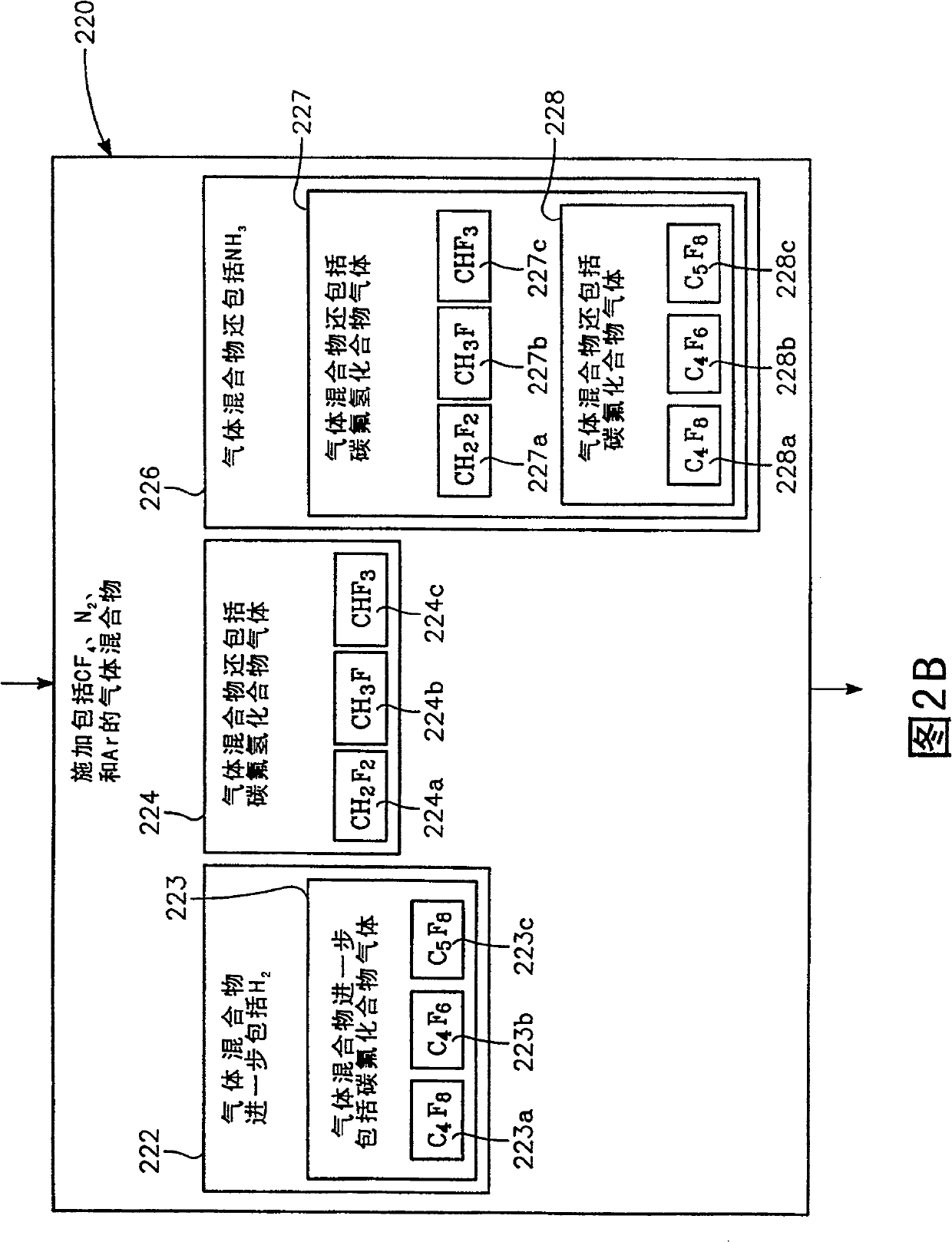

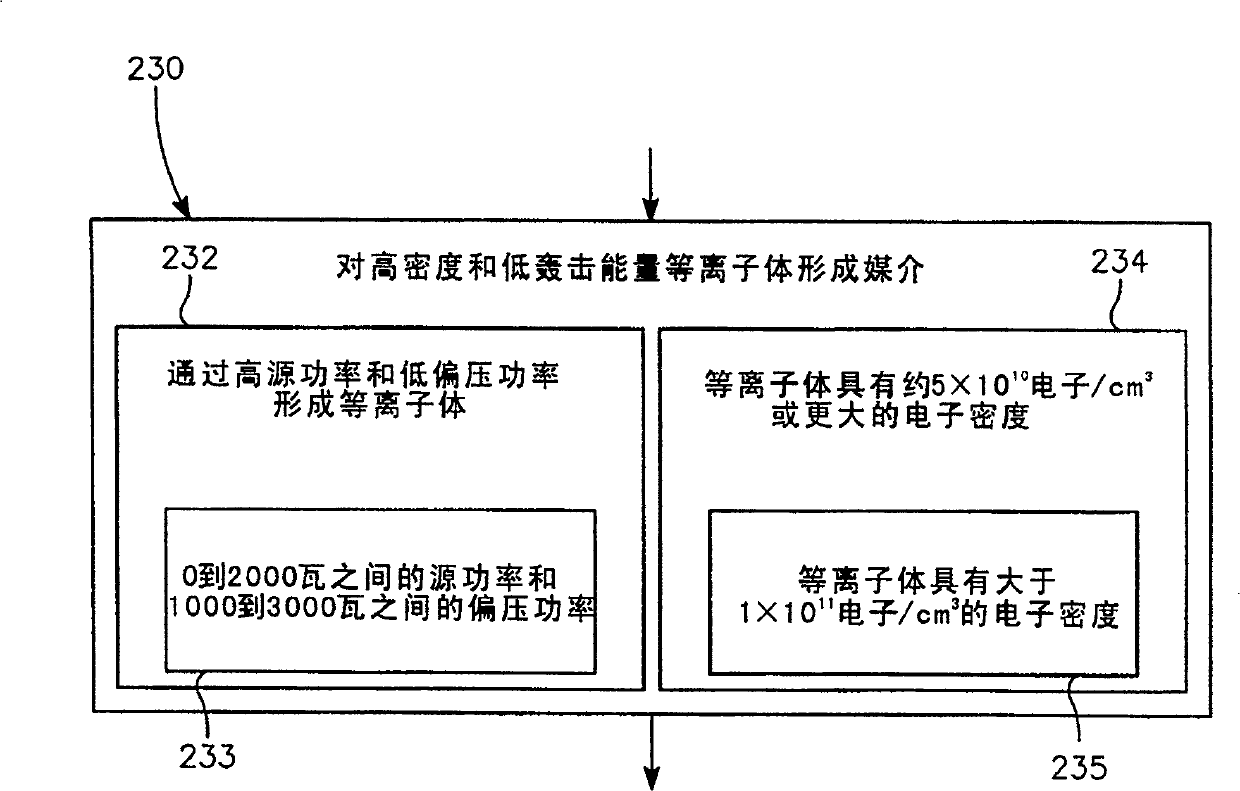

[0084] An example of an embodiment of the present invention includes more than Etching at high source and low bias settings with a gas mixture containing tetrafluoromethane, nitrogen, and argon. A 300 mm diameter wafer was used in this example. Figure 5A The cross-sectional views of A and B show example completed etched structures.

[0085] The first step of the etching step of Example 1 is to provide the structure to be etched. Such as Figure 4 As shown, the structure 400 of this example includes a barrier layer 410, an interlayer dielectric layer (ILD) 420 on the barrier layer 410, an antireflective dielectric layer (DARC) 430 on the ILD layer 420, and a bottom layer on the DARC layer 430. Antireflection layer (BARC) 440 , and photoresist layer (PR) 450 on BARC layer 440 .

[0086] Barrier layer 410 in this example is Blok II (SiC), which acts as an etch stop layer as described above. As mentioned above, the dielectric material of the ILD layer 420 is black diamond S...

example 2

[0105] An example of another embodiment of the present invention includes using a plateau and low bias, a gas mixture comprising tetrafluoromethane, nitrogen, argon, and hydrogen, to rate etching. This example uses a 300mm diameter wafer. Figure 6A The cross-sections of and B show the structure formed by this example.

[0106] The first step of the method of this example is to provide a structure that will be etched in the following steps. The layers of the structure used in this example are arranged in Figure 4 Same as in Example 1 above shown.

[0107] Structure 400 is etched using an Applied Centura Enabler etch tool. This example performs a two-part etch process, including arc etch and main etch. This two-part etch process allows etching to be made to the specific material or material being etched. During arc etching, each of BARC layer 440 and DARC layer 430 is etched through each opening defined in photoresist layer 450 . Next, during the main etch, the ILD lay...

example 3

[0117] Another example of the present invention is such an etching process: by using high source and low bias voltage and including tetrafluoromethane (CF 4 ), nitrogen (N 2 ), argon (Ar) and hydrogen (H 2 ) of the gas mixture, a measured value greater than the etching rate. As in Example 2, this example differs in that a shorter main etch time is used. Also, the etch stops before the via or trench reaches the barrier layer. Again, a 300 mm diameter wafer was used. Figure 7A and B show cross-sectional views of structures formed by this example.

[0118] The layers of the structure used in this example are arranged in Figure 4 Same as in Example 1 above shown.

[0119] The structures were etched using the Applied Centrua Enabler etch tool described above. Etching is two parts, including arc etch and main etch. During the arc etch, each of the BARC layer 440 and the DARC 430 layer 440 is etched, and during the main etch, the ILD layer 420 is etched with the etch term...

PUM

| Property | Measurement | Unit |

|---|---|---|

| diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com