Flux-free chip to wafer joint serial thermal processor arrangement

a thermal processor and chip technology, applied in the field of electronic chips, can solve the problems of reducing the reliability of the device produced, the inability to perfectly clean the die and the wafer, and the removal of flux, so as to reduce the surface oxides of lead, tin, copper and silver. the effect of reducing the voids

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

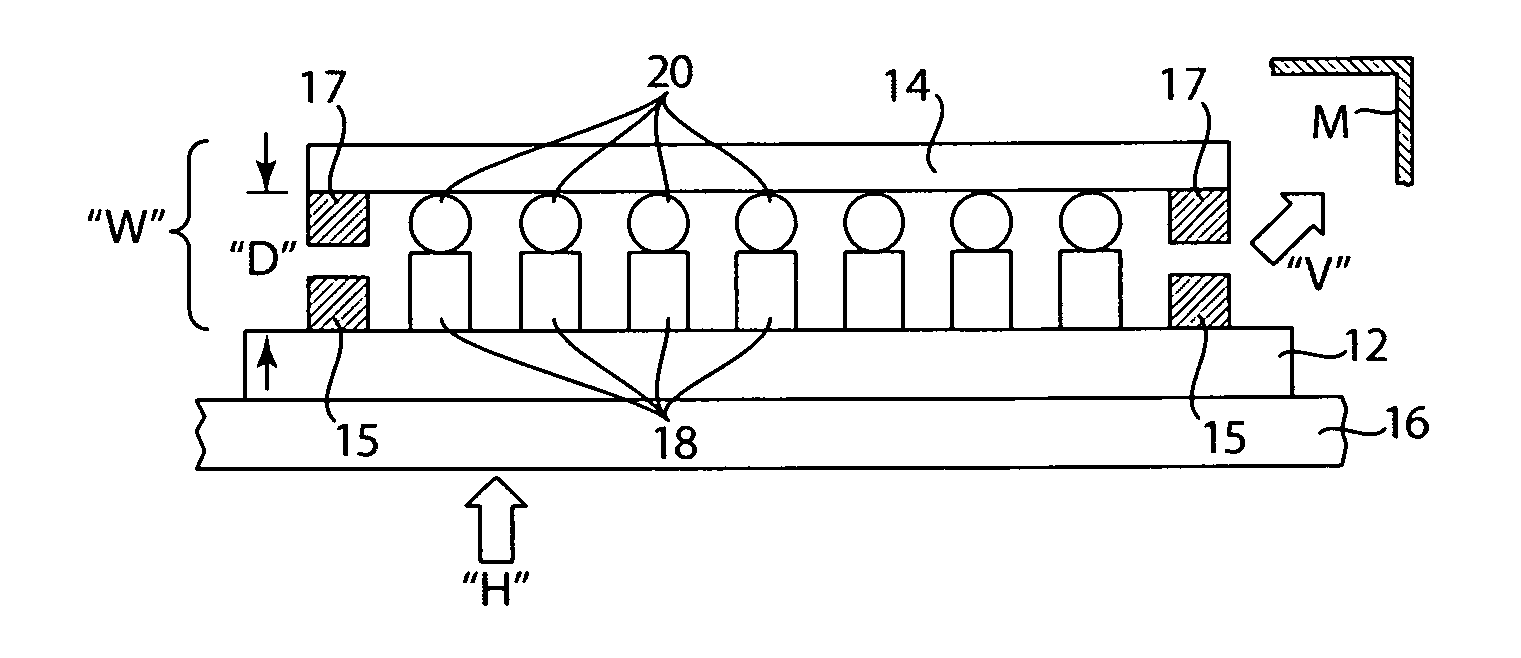

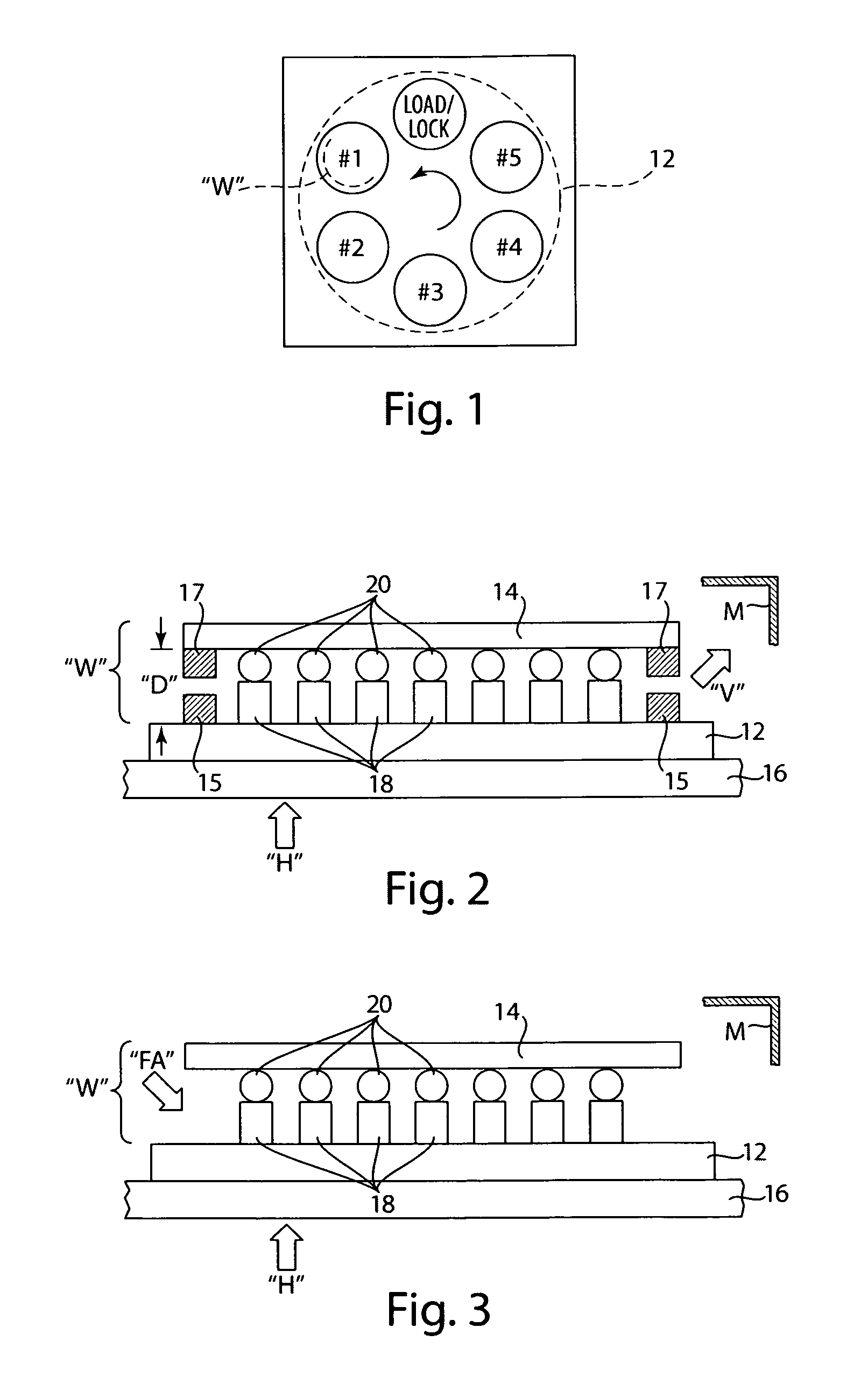

[0047]The invention a an electronic chip and chip manufacturing process which comprises a rotatable, circumferentially organized, serial thermal processing station arrangement 10 using a method for serially treating a pre-assembled chip or die and a wafer assembly “W” through a series of preferably at least six independent, enclosed station chambers in the processor arrangement 10, as represented in FIG. 1.

[0048]The rotary production station arrangement 10 is arranged to rotate so as to present a material to be treated, such as a semiconductor wafer, at a series of circumferentially spaced-apart locations, from a Load / Lock station to processing stations numbered 1 through 5, which stations each are arranged to independently control the temperature, pressure and atmosphere thereat, as is similarly represented in various aspects and embodiments of the arrangement 10, in a mechanism as may be shown in the above-identified '789 and '879 patents, incorporated by reference herein.

[0049]Th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| temperature | aaaaa | aaaaa |

| pressure | aaaaa | aaaaa |

| melting temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com