Memory embedded logic semiconductor device having memory region and logic circuit region

a technology of logic circuit and memory region, which is applied in the direction of semiconductor devices, basic electric elements, electrical appliances, etc., can solve the problems of increased connection resistance, high manufacturing cost, and difficulty in thinning down, so as to reduce the connection resistance between the capacitor and the first diffusion region of the cell transistor, prevent short circuit, and reduce the effect of manufacturing cos

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034]The invention will be now described herein with reference to illustrative embodiments. Those skilled in the art will recognize that many alternative embodiments can be accomplished using the teachings of the present invention and that the invention is not limited to the embodiments illustrated for explanatory purposes.

[0035]Hereinafter, the embodiment of the invention will be described with reference to the accompanying drawings. In all the drawings, like elements are referenced by like reference numerals and descriptions thereof will not be repeated.

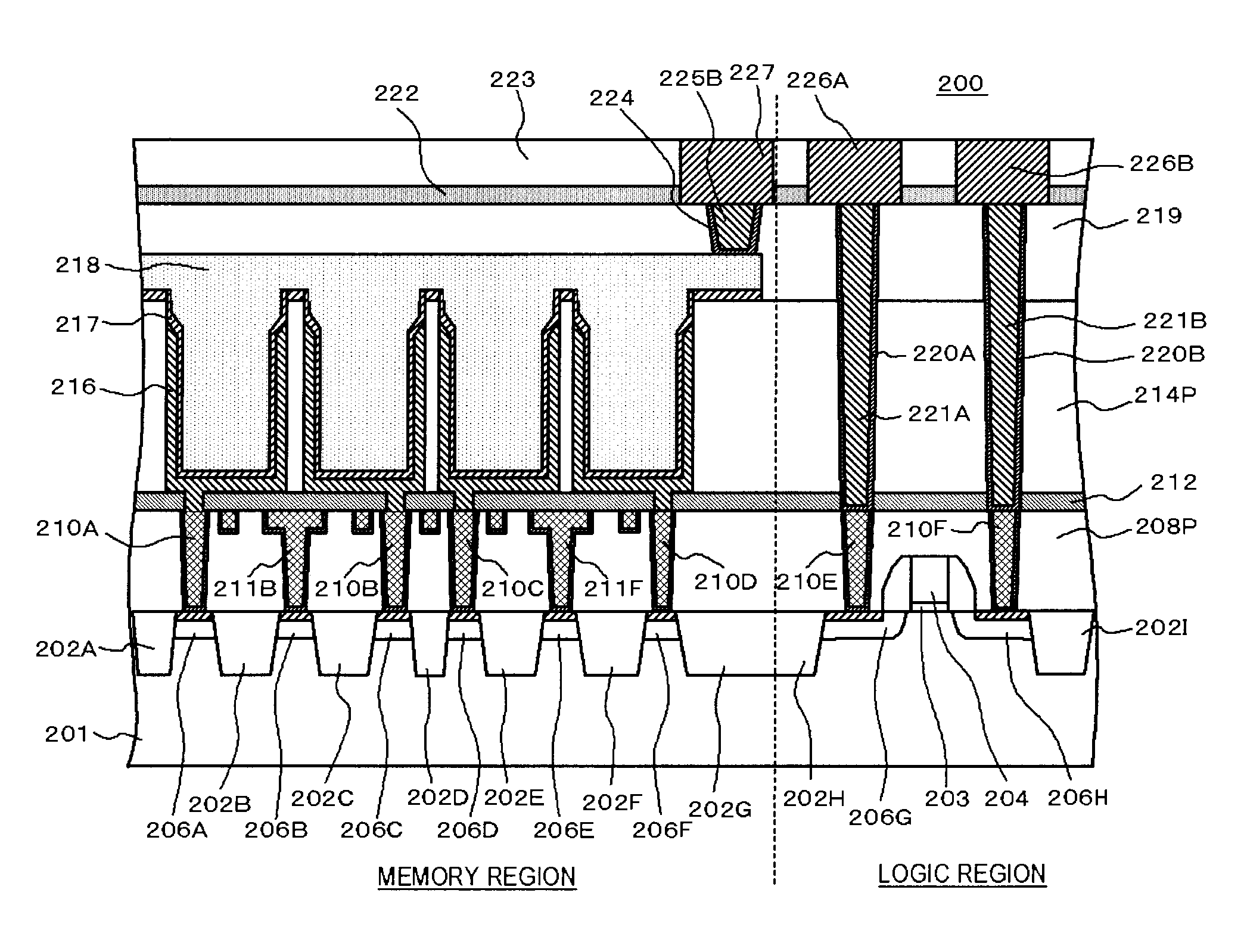

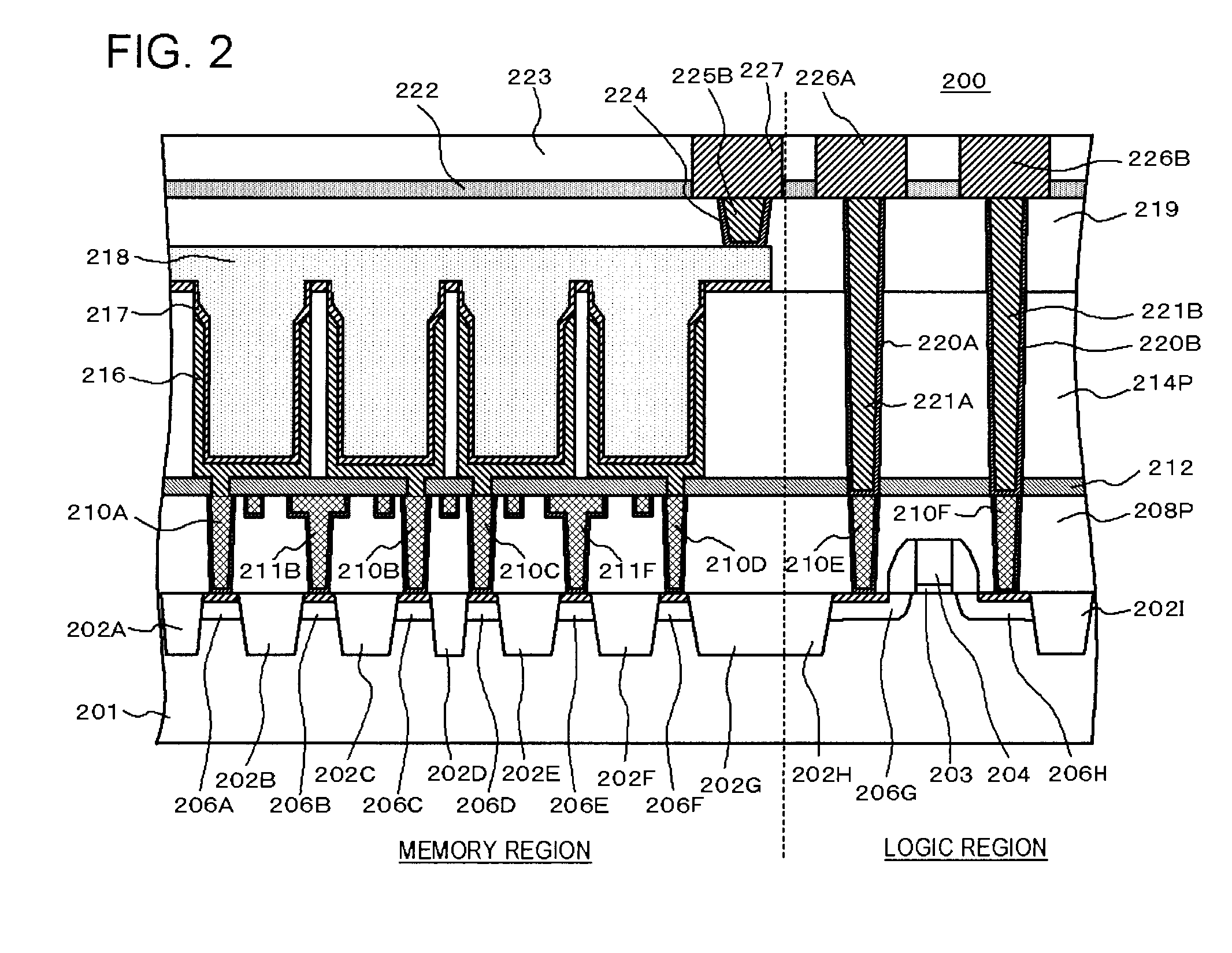

[0036]FIG. 2 is a cross-sectional view illustrating the schematic configuration of a semiconductor device 200 according to an embodiment of the invention. The semiconductor device 200 includes a cell transistor (not shown) formed in a memory region of a semiconductor substrate 201, and a logic device formed in a logic region of the semiconductor substrate 201. This logic device includes a logic transistor. In FIG. 2, the logic tra...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com