Method of forming thin-film transistor devices with electro-static discharge protection

a technology of thin-film transistors and electrostatic discharge protection, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of static electricity accumulation that cannot be cancelled, reduce product yield, and damage to devices, so as to improve product yield and device reliability, maintain the aperture ratio of products, and the smoothness of the passivation layer is not affected

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

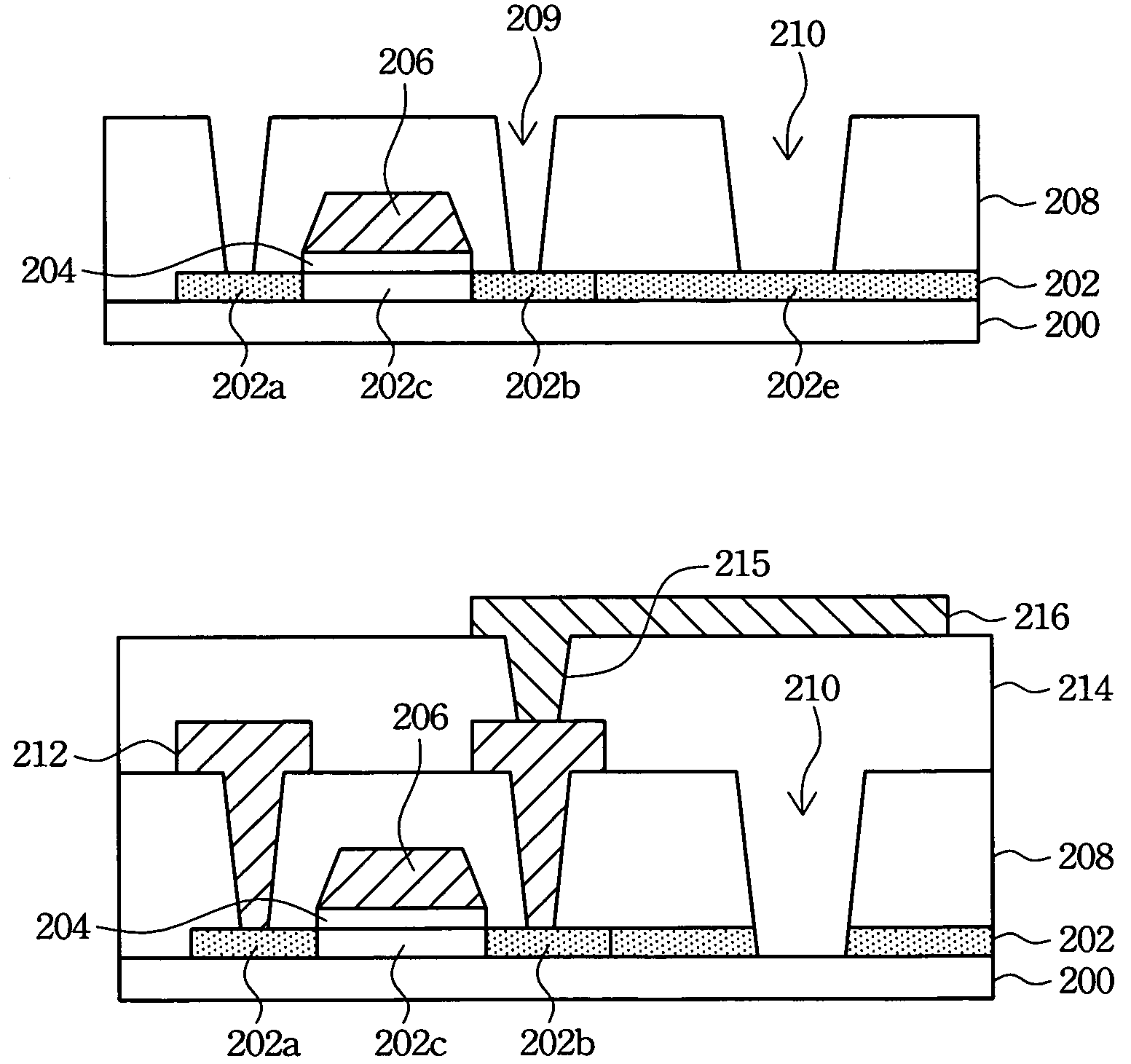

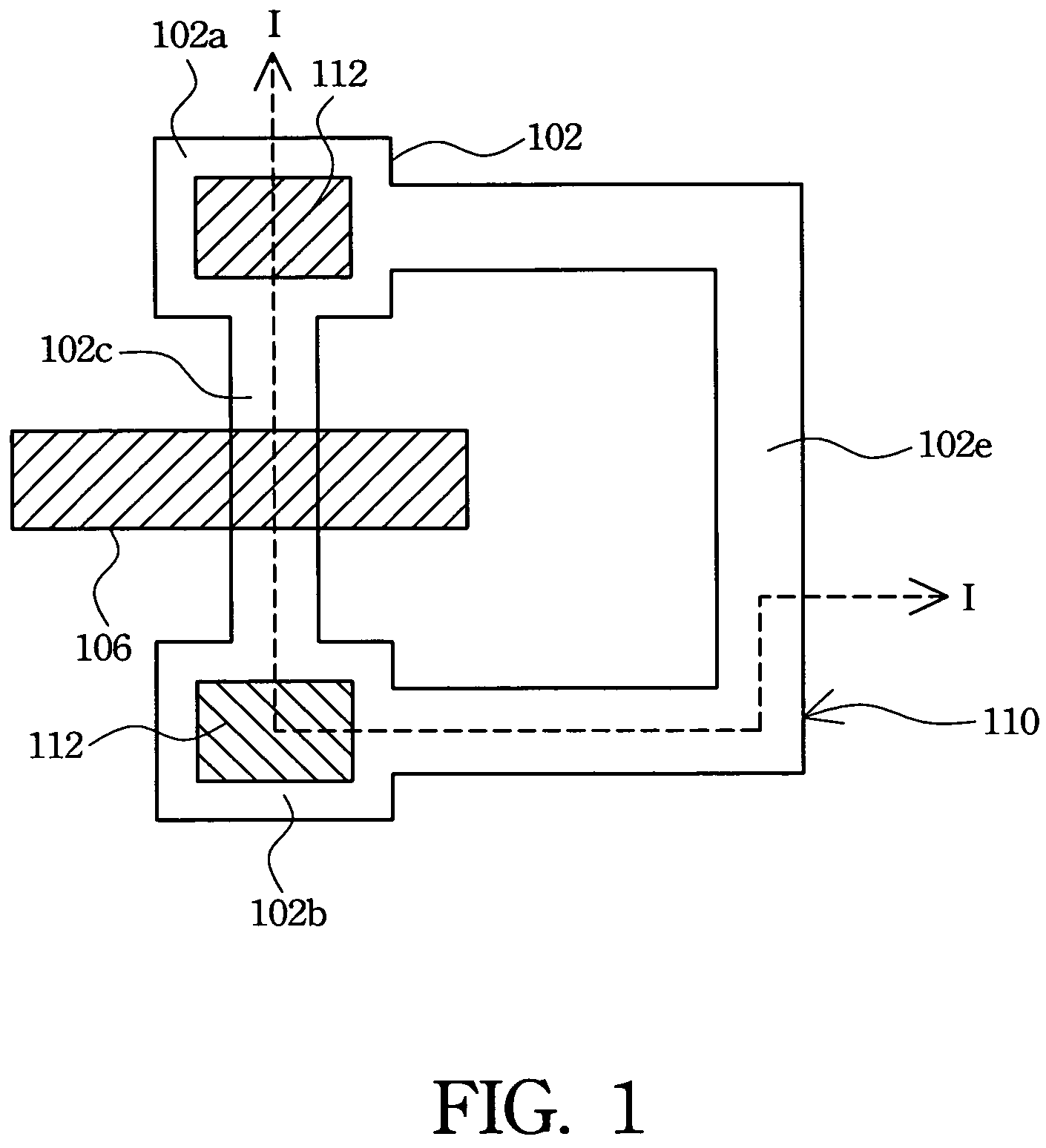

[0022]The present invention discloses a method of forming TFT devices with ESD protection and a structure thereof. Referring to FIG. 1 and FIGS. 2A–2C respectively. FIG. 1 is a top view of a TFT in accordance with the first preferred embodiment of the present invention, and FIGS. 2A–2C are cross-sectional schematic diagrams showing the process for forming the TFT in accordance with the first preferred embodiment of the present invention. The cross-sectional structure shown in FIGS. 2A–2C is taken along line I—I in FIG. 1.

[0023]A source region is connected with a drain region to form a short circuit by utilizing a pattern design for a poly-Si layer. Referring to FIG. 1, in addition to the source region 102a, the drain region 102b and a channel region 102c, a connector 102e connecting the source region 102a and the drain region 102b is also formed in the poly-Si layer 102 to construct the short circuit for dispersing static electricity accumulated in TFT fabrication. Further, a gate e...

embodiment 2

[0033]The present invention discloses another method of forming TFT devices with ESD protection and a structure thereof. Reference is made to FIG. 3, FIG. 4 and FIGS. 5A–5C respectively. FIG. 3 is a partial array structure of the display devices in accordance with the second preferred embodiment of the present invention, FIG. 4 is a top view of TFT devices in accordance with the second preferred embodiment of the present invention, and FIGS. 5A–5C are cross-sectional schematic diagrams showing the process for forming the TFT devices in accordance with the second preferred embodiment of the present invention. The cross-sectional structure shown in FIGS. 5A–5C is taken along line II—II in FIG. 4.

[0034]A TFT in a pixel is connected electrically with another TFT in another pixel by pattern design for a poly-Si layer to form a short circuit. Referring to FIG. 3, regions controlled by data lines 318 and scan lines 319 represent pixels, and a TFT 322 in a pixel 320 is connected with a TFT ...

embodiment 3

[0042]Because ESD protection is achieved by the first embodiment or the second embodiment for forming TFT devices, the present invention discloses further a method of forming TFT devices with ESD protection by combining the first embodiment and the second embodiment for optimized ESD protection.

[0043]Reference is made to FIG. 6 and FIG. 7, respectively. FIG. 6 is a partial array structure of the display devices in accordance with the third preferred embodiment of the present invention, and FIG. 7 is a top view of TFT devices in accordance with the third preferred embodiment of the present invention.

[0044]A source region is connected electrically with a drain region in each TFT to form short circuits, and a TFT in a pixel is also connected electrically with another TFT in another pixel to form another short circuit. Referring to FIG. 6, regions controlled by data lines 618 and scan lines 619 represent pixels, and a TFT 622 in a pixel 620 is connected electrically with a TFT 642 in a ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| current | aaaaa | aaaaa |

| voltage | aaaaa | aaaaa |

| resolution loss | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com