Accelerating garbage collection of flushed logical erase blocks in non-volatile memory

a non-volatile memory and garbage collection technology, applied in the direction of memory adressing/allocation/relocation, instruments, input/output to record carriers, etc., can solve the problem of ineligible garbage collection, reduce overprovisioning, reduce overprovisioning, and mitigate certain cell-to-cell interference characteristics of memory

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

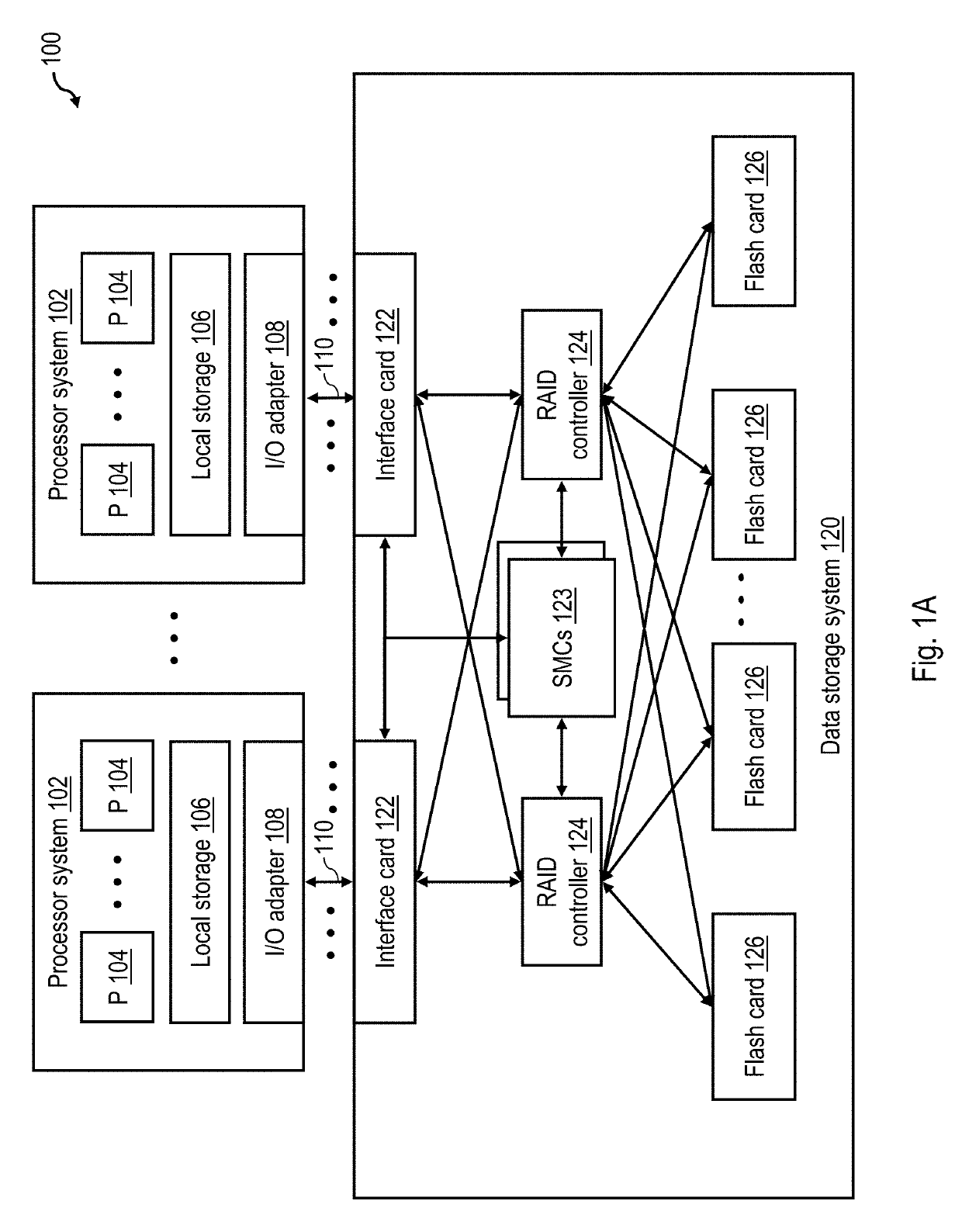

[0017]With reference to the figures and with particular reference to FIG. 1A, there is illustrated a high level block diagram of an exemplary data processing environment 100 including a data storage system 120 having a non-volatile memory array as described further herein. As shown, data processing environment 100 includes one or more hosts, such as a processor system 102 having one or more processors 104 that process instructions and data. A processor system 102 may additionally include local storage 106 (e.g., dynamic random access memory (DRAM) or disks) that may store program code, operands and / or execution results of the processing performed by processor(s) 104. In various embodiments, a processor system 102 can be, for example, a mobile computing device (such as a smartphone or tablet), a laptop or desktop personal computer system, a server computer system (such as one of the POWER series of servers available from International Business Machines Corporation), or a mainframe co...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com